REFERENCE DESIGN PMC-1990815

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

**VORTEX CHIPSET**

# DSLAM REFERENCE DESIGN: CORE CARD

## RELEASED

### Issue 4

## December 2000

© 2000 PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 Phone 604.415.6000 FAX 604.415.6200

This document is for the internal use of PMC-Sierra, Inc. and PMC-Sierra, Inc. customers only.

In any event, no part of this document may be reproduced in any form without the express written consent of PMC-Sierra, Inc.

**ISSUE 4**

DSLAM REFERENCE DESIGN: CORE CARD

REFERENCE DESIGN PMC-1990815

#### **REVISION HISTORY**

| Issue Issue Date Details of Change No.                                                                                                                                                       |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2000 consistency with software driv<br>Updated LVDS hot swap exp<br>may be affected by setting OC<br>S/UNI-DUPLEX. Register wr<br>enable OCAEN at the very er<br>sequence is already impleme |                  | Replaced "metadriver" with "VORTEX Chipset Driver" for<br>consistency with software driver documents.<br>Updated LVDS hot swap explanation and cell transfer, which<br>may be affected by setting OCAEN bit in register 0x0A of the<br>S/UNI-DUPLEX. Register write sequence is required to<br>enable OCAEN at the very end of the chipset activation. The<br>sequence is already implemented with the VORTEX Chipset<br>Driver on CD-ROM Ver 3.0. |  |  |

| 3                                                                                                                                                                                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 2                                                                                                                                                                                            | December<br>1999 | Paper design errata-document. This Reference Design<br>Issue 2 has no Core Card PCB manufactured.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 1 August 1999 First Issue. Core Card Issue 1 build.                                                                                                                                          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

© 2000 PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 Phone 604.415.6000 FAX 604.415.6200

This document is for the internal use of PMC-Sierra, Inc. and PMC-Sierra, Inc. customers only.

In any event, no part of this document may be reproduced in any form without the express written consent of PMC-Sierra, Inc.

REFERENCE DESIGN PMC-1990815 PMC-Sierra, Inc.

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### **CONTENTS**

| 1. | OVERV  | /IEW    | 1                                        |   |

|----|--------|---------|------------------------------------------|---|

| 2. | DSLAN  | I CORE  | CARD FEATURES2                           |   |

| 3. | TYPICA | AL DSLA | M APPLICATION WITH CORE CARD3            | ; |

|    | 3.1.   | Compa   | ct PCI (cPCI) Development Shelf4         | ŀ |

|    | 3.2.   | DSLAM   | Reference Design Core Card Architecture4 | Ļ |

| 4. | CORE   | CARD F  | UNCTIONAL EXPLANATION7                   | , |

|    | 4.1.   | Core Ca | ard Block Diagram7                       | , |

|    |        | 4.1.1.  | Block Diagram Drawing                    | • |

|    |        | 4.1.2.  | VORTEX Chipset                           | ; |

|    |        | 4.1.3.  | LVDS Interface                           | ; |

|    |        | 4.1.4.  | PCI Bridge9                              | ) |

|    |        | 4.1.5.  | Hot Swap Controller9                     | ) |

|    |        | 4.1.6.  | Ejector Handle and LED9                  | ) |

|    |        | 4.1.7.  | CPLD9                                    | ) |

|    |        | 4.1.8.  | RAMs10                                   | ) |

|    | 4.2.   | DSLAM   | I High-Speed LVDS Serial Interface11     |   |

|    |        | 4.2.1.  | Example of LVDS Routing on Core Card 11  |   |

|    |        | 4.2.2.  | LVDS Transmitters vs. Hot Swap           |   |

|    | 4.3.   | 8kHz In | terface12                                | ) |

| 5. | CORE   | CARD C  | HIPSET OVERVIEW15                        | , |

|    | 5.1.   | PM7324  | 4 S/UNI-ATLAS                            | ; |

|    |        | 5.1.1.  | Ingress SRAM16                           | ; |

|    |        | 5.1.2.  | Egress RAM                               | ; |

|    | 5.2.   | S/UNI-A | APEX                                     | ) |

|    |        | 5.2.1.  | Functional Description                   | ) |

|    |        | 5.2.2.  | Context Memory SSRAM Interface23         | ; |

|    |        | 5.2.3.  | Cell Buffer SDRAM Interface24            | Ļ |

|    | 5.3.   | S/UNI-\ | /ORTEX                                   | ; |

|    | 5.4.   | S/UNI-E | DUPLEX                                   | ; |

|    | 5.5.   | CPCI B  | ridge29                                  | ) |

|    |        |         |                                          |   |

REFERENCE DESIGN PMC-1990815

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

|    |       | 5.5.1. PCI9054 PCI Bridge                                             |

|----|-------|-----------------------------------------------------------------------|

|    |       | 5.5.2. SEEP Basics                                                    |

| 6. | SIGN  | AL FLOW ON THE CORE CARD IN BRIEF                                     |

|    | 6.1.  | Upstream Direction                                                    |

|    | 6.2.  | Downstream Direction                                                  |

| 7. | HOT S | SWAP                                                                  |

|    | 7.1.  | cPCI and Power Rail Hot Swap32                                        |

|    | 7.2.  | LVDS Hot Swap34                                                       |

|    | 7.3.  | Blue LED and Microswitch Control35                                    |

| 8. | CPCI  | INTERFACE, PCI BRIDGE AND CPLD                                        |

|    | 8.1.  | Control Interface Block Diagram                                       |

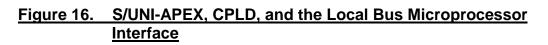

|    | 8.2.  | PCI Bridge – CPLD Interface                                           |

|    | 8.3.  | Major Control Lines Between S/UNI-APEX, CPLD and PCI9054 Interface 38 |

|    | 8.4.  | Address Mapping40                                                     |

|    | 8.5.  | PLX PCI9054 Address Spaces41                                          |

|    | 8.6.  | Card ID Number                                                        |

|    | 8.7.  | Serial EEPROM Load Registers41                                        |

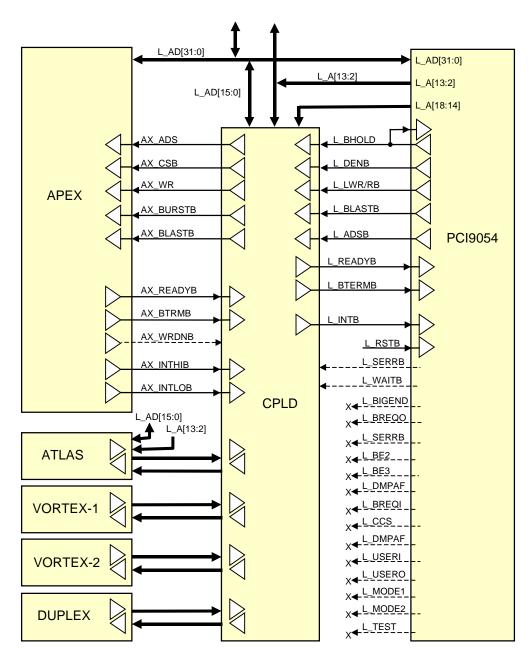

|    | 8.8.  | CPLD                                                                  |

|    |       | 8.8.1. Local Bus Memory Map45                                         |

|    |       | 8.8.2. CPLD Registers                                                 |

|    |       | 8.8.3. Alarms And Interrupts                                          |

|    |       | 8.8.4. 8 kHz Channel                                                  |

|    |       | 8.8.5. Address Decoding and Chip Enable                               |

|    |       | 8.8.6. CPLD Type                                                      |

|    | 8.9.  | CPLD Block Diagram                                                    |

| 9. | CONN  | ECTORS ON CORE CARD                                                   |

|    | 9.1.  | CPCI Connectors                                                       |

|    |       | 9.1.1. J1 on Core Card51                                              |

|    |       | 9.1.2. J2, J3, and J4 on Core Card51                                  |

|    |       | 9.1.3. J5 on Core Card                                                |

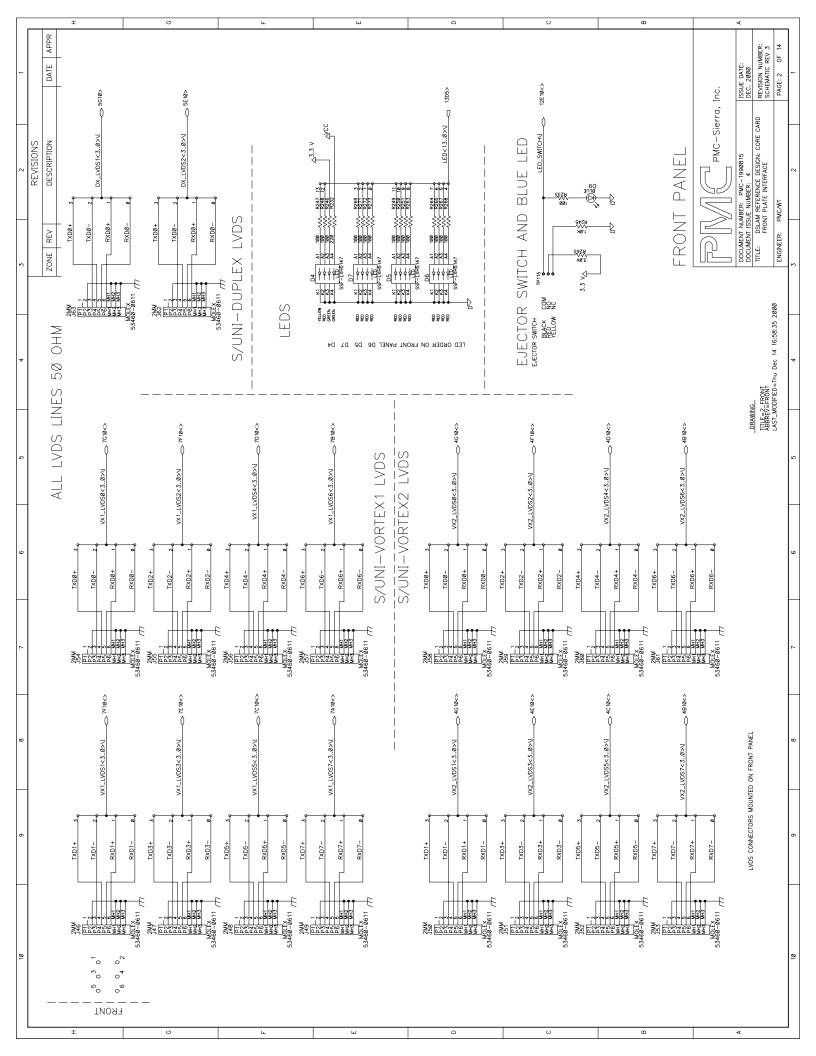

|    | 9.2.  | LVDS Interface on the LVDS-backlane51                                 |

|    | 9.3.  | LVDS Interface on the Front Panel52                                   |

REFERENCE DESIGN PMC-1990815

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

|     | 9.4.  | CPLD Programming Interface on J34          | 52 |

|-----|-------|--------------------------------------------|----|

|     | 9.5.  | 25 MHz Output on J45                       | 52 |

|     | 9.6.  | RESET Header J64                           | 52 |

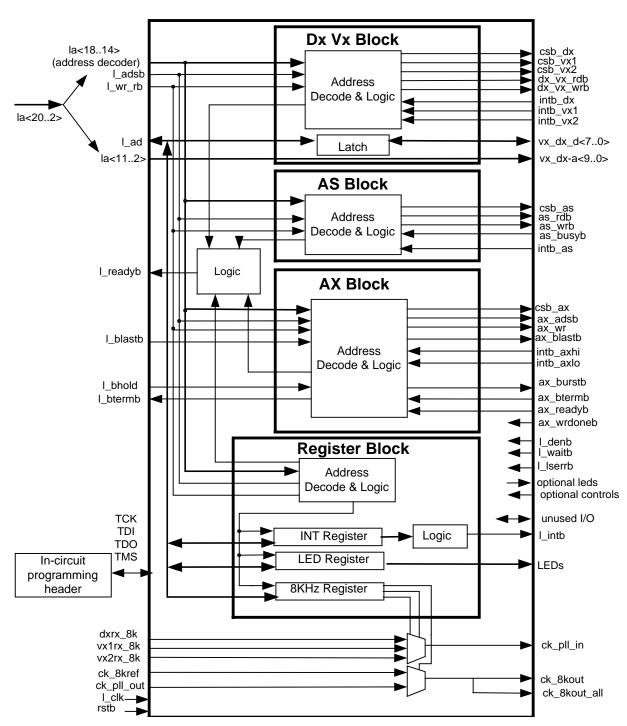

|     | 9.7.  | 8 kHz Interface on J65 and J72             | 52 |

|     | 9.8.  | JTAG Interface on J66                      | 53 |

|     | 9.9.  | Mictor Connectors J70 and J71              | 53 |

|     | 9.10. | Clock Control Header J73                   | 53 |

|     | 9.11. | Optional Reset to CPLD Header J74          | 53 |

|     | 9.12. | Ejector Handle Switch Header TP115         | 54 |

|     | 9.13. | Miscellaneous Test Points                  | 54 |

| 10. | LVDS  | INTERFACE                                  | 55 |

|     | 10.1. | LVDS Front Panel Interface                 | 55 |

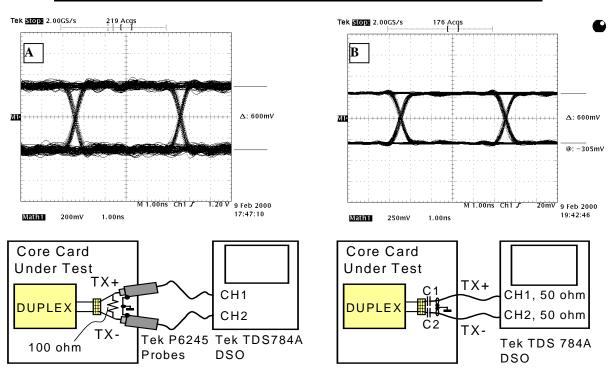

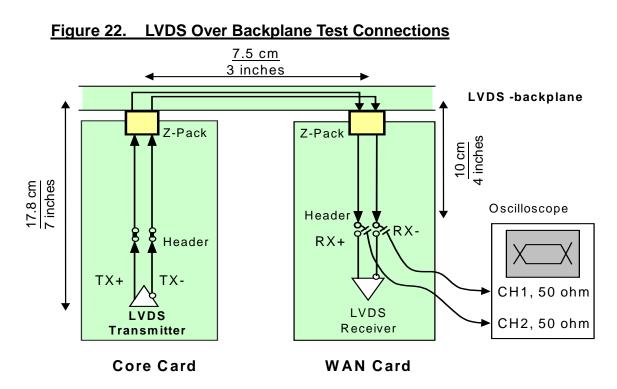

|     | 10.2. | LVDS Eye Pattern at Jumper Field Tests     | 57 |

|     | 10.3. | LVDS Eye Pattern over LVDS-Backplane Tests | 58 |

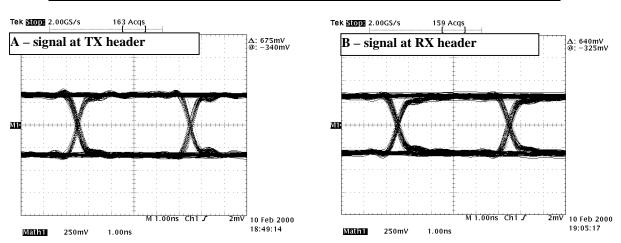

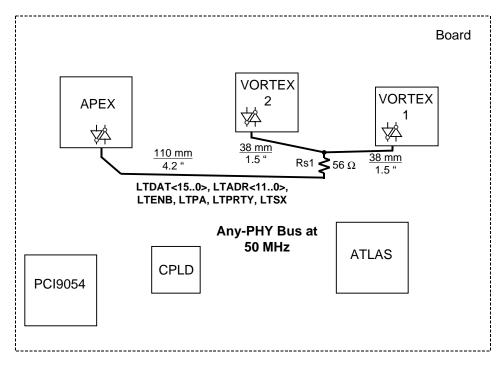

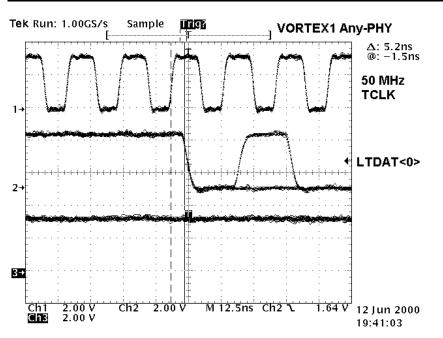

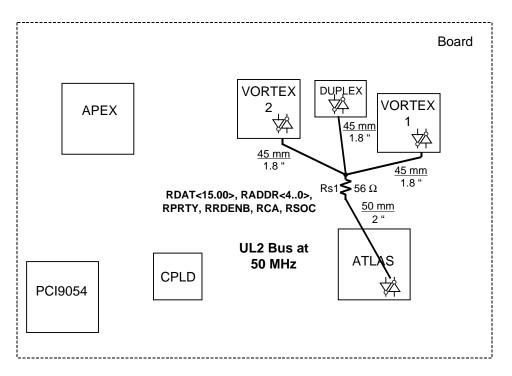

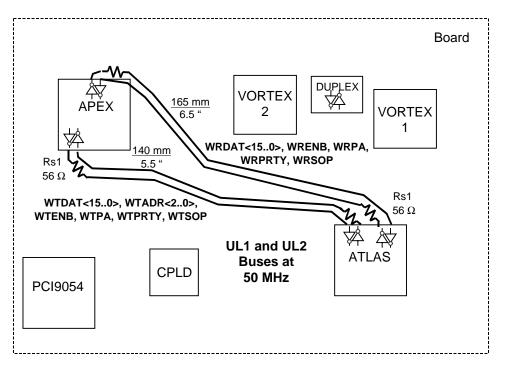

| 11. | BUS T | ERMINATION EXAMPLES                        | 61 |

|     | 11.1. | Microprocessor Bus Termination             | 61 |

|     | 11.2. | Downstream Any-PHY Bus Termination         | 63 |

|     | 11.3. | Upstream/Downstream UL2 Bus Termination    | 64 |

|     | 11.4. | S/UNI-APEX – S/UNI-ATLAS Bus Termination   | 66 |

|     | 11.5. | RAM Bus Termination                        | 67 |

| 12. | HARD  | WARE                                       | 74 |

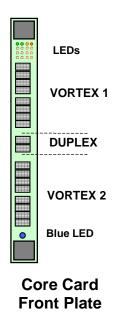

|     | 12.1. | Card Form                                  | 74 |

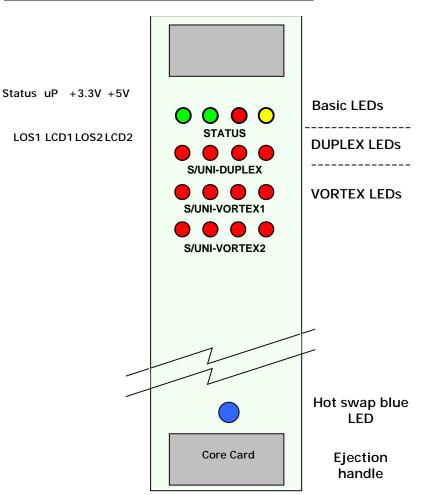

|     | 12.2. | Front Plate on Core Card                   | 74 |

|     | 12.3. | LEDs On the Front Plate                    | 75 |

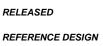

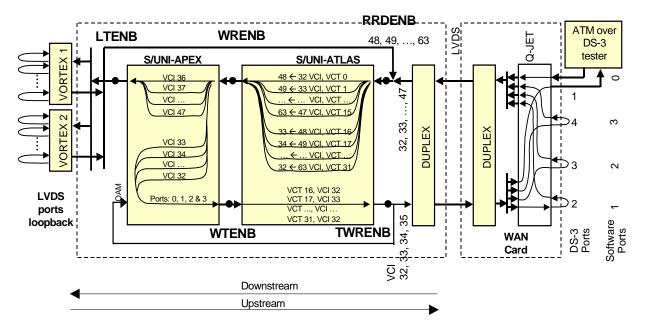

|     | 12.4. | Printed Circuit Board Stack                | 77 |

|     | 12.5. | Key Coding on the J1 Connector             | 78 |

|     | 12.6. | Power Supply Specification                 | 78 |

|     |       | 12.6.1. Core Card                          | 78 |

|     |       | 12.6.2. S/UNI-DUPLEX and S/UNI-VORTEX      | 79 |

| 13. | SOFT  | WARE                                       | 80 |

|     | 13.1. | System Processor Requirement               | 80 |

|     | 13.2. | DSLAM Operating System                     | 80 |

|     |       |                                            |    |

ISSUE 4

**VORTEX CHIPSET**

REFERENCE DESIGN PMC-1990815

DSLAM REFERENCE DESIGN: CORE CARD

|     | 13.3. | Device Drivers                                              |     |

|-----|-------|-------------------------------------------------------------|-----|

|     | 13.4. | Example of VORTEX Chipset Setup                             |     |

|     |       | 13.4.1. APEX Setup                                          |     |

|     |       | 13.4.2. APEX Operations                                     | 81  |

|     |       | 13.4.3. DUPLEX and VORTEX Setup                             | 81  |

|     |       | 13.4.4. DUPLEX And VORTEX Operation                         | 81  |

|     |       | 13.4.5. ATLAS Setup                                         | 81  |

|     |       | 13.4.6. ATLAS Operations                                    |     |

|     |       | 13.4.7. Important Notes For Chipset Level Setup             | 82  |

|     | 13.5. | Firmware                                                    | 82  |

|     | 13.6. | Programmable Logic Devices                                  |     |

|     | 13.7. | System Control                                              |     |

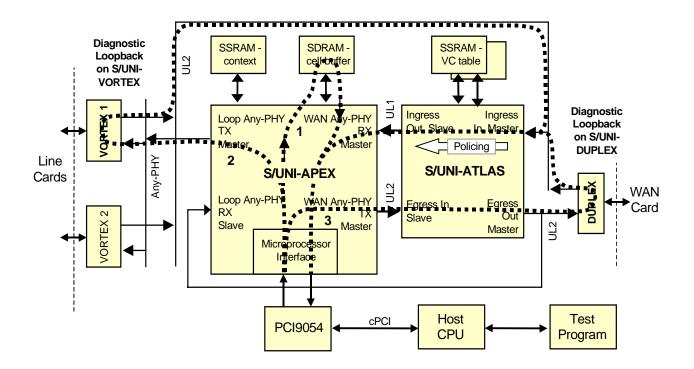

| 14. | APPE  | NDIX A: TESTS EXAMPLE UTILIZING CORE CARD DRIVER            |     |

|     | 14.1. | Register and RAM Test with VORTEX Chipset Driver            |     |

|     | 14.2. | Cell Data Path with Internal Loopback Test                  |     |

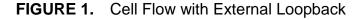

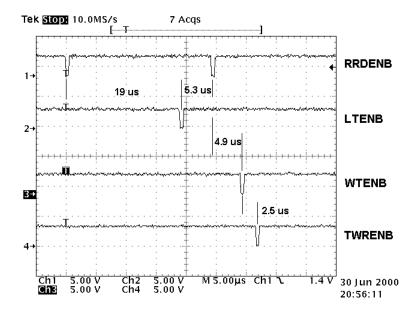

|     | 14.3. | External Loopback Test                                      |     |

|     |       | 14.3.1. Sub Test 1: Downstream/Upstream on Sixteen Channels | 87  |

| 15. | APPE  | NDIX B: VOLTAGE DISCHARGE ON TRI-STATED BUS                 | 92  |

| 16. | APPE  | NDIX C: EXAMPLE OF SEEP READING ON RESET                    | 95  |

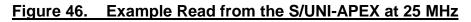

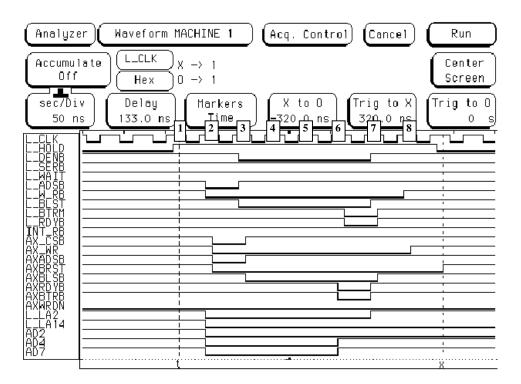

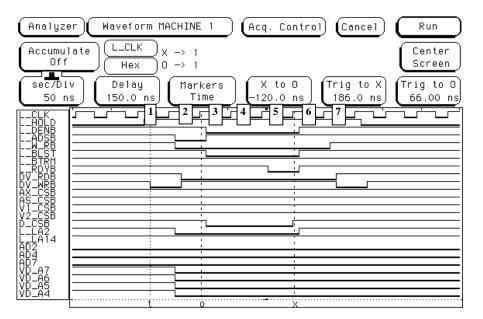

| 17. | APPE  | NDIX D: LOCAL BUS TIMING EXAMPLES                           | 96  |

|     |       | 17.1.1. Timing Example for Read from S/UNI-APEX             |     |

|     |       | 17.1.2. Timing Example for Write to S/UNI-APEX              | 97  |

|     |       | 17.1.3. Timing Example for Read from S/UNI-DUPLEX           |     |

|     |       | 17.1.4. Timing Example for Write to S/UNI-DUPLEX            |     |

| 18. | APPE  | NDIX E: VHDL FOR CPLD                                       |     |

| 19. | APPE  | NDIX F: BILL OF MATERIAL                                    |     |

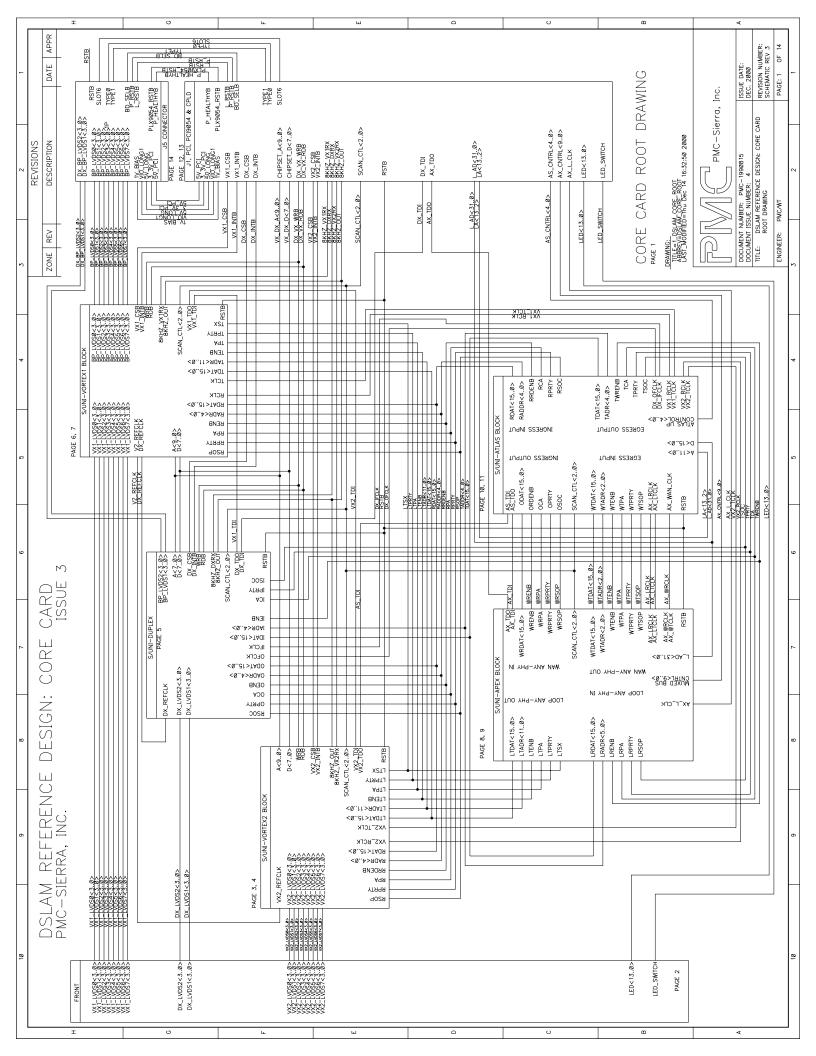

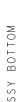

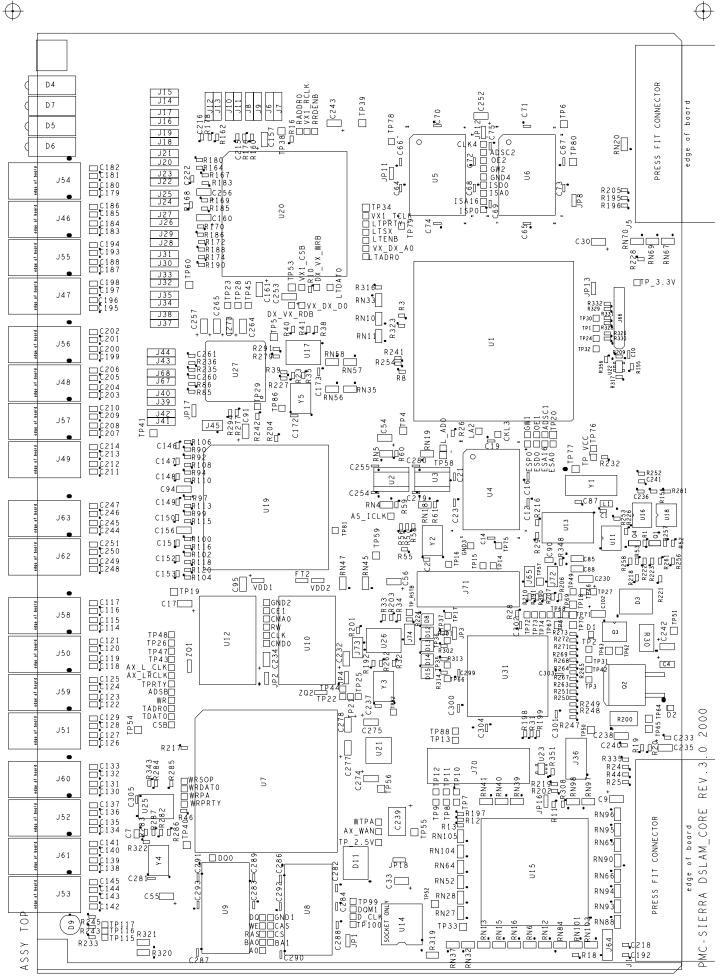

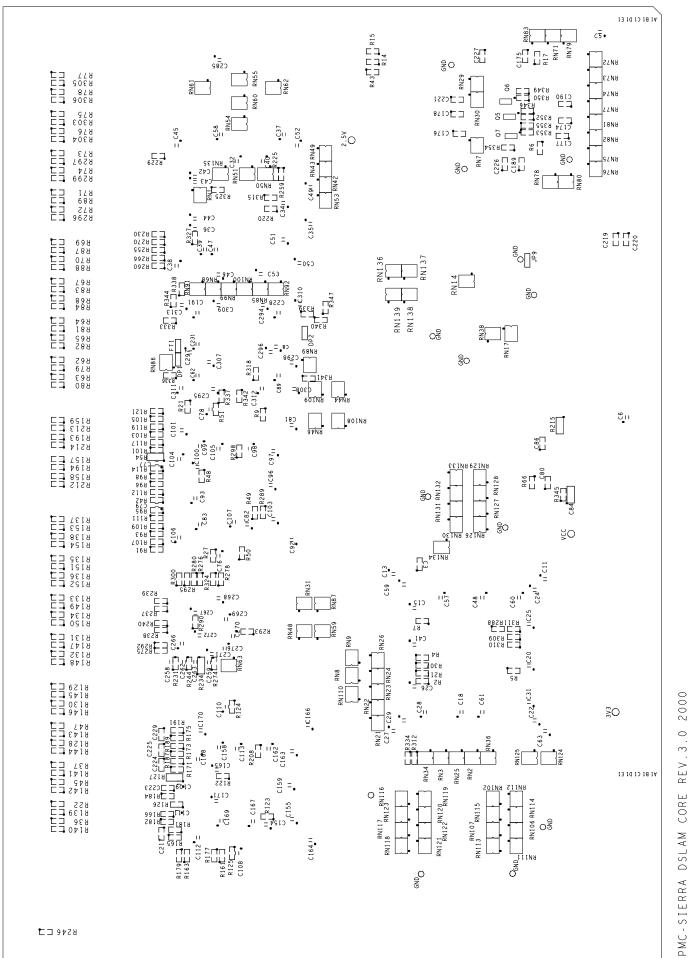

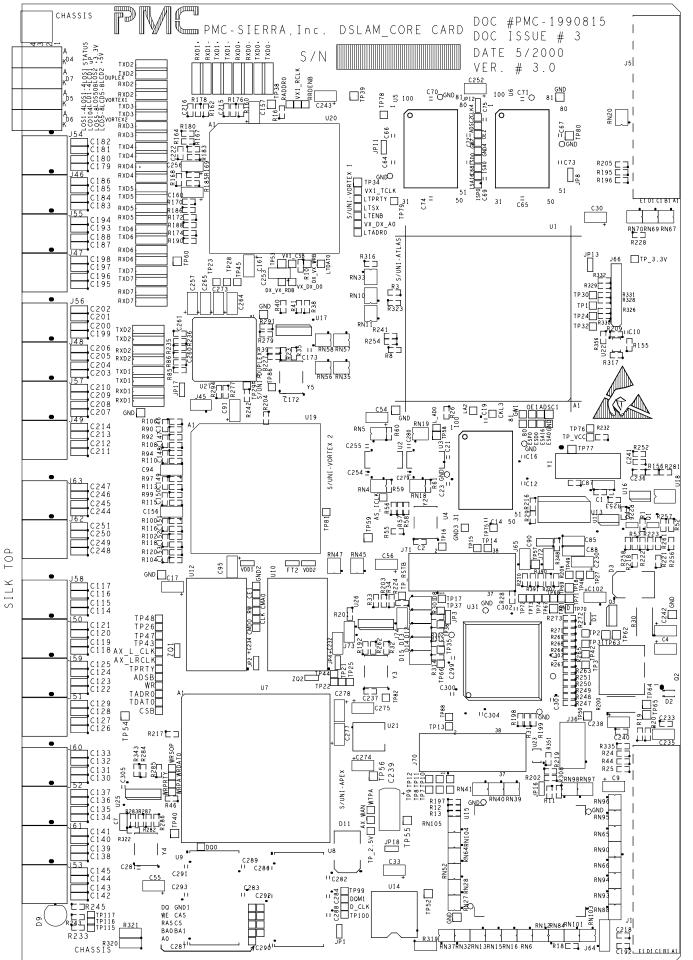

| 20. | APPE  | NDIX G: SCHEMATIC DIAGRAMS                                  | 113 |

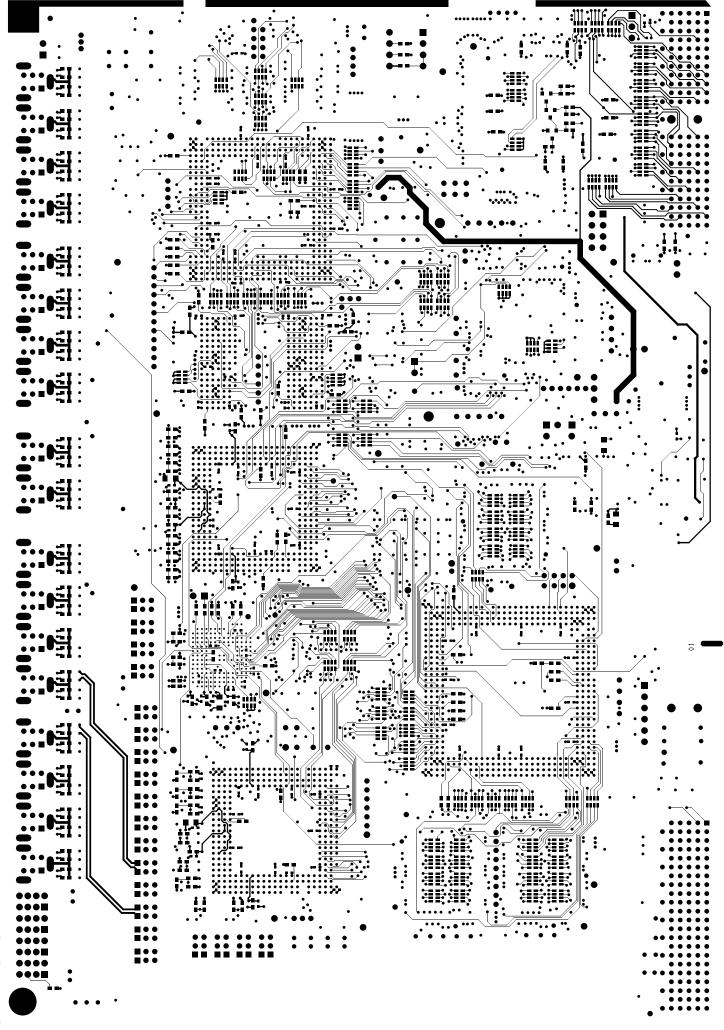

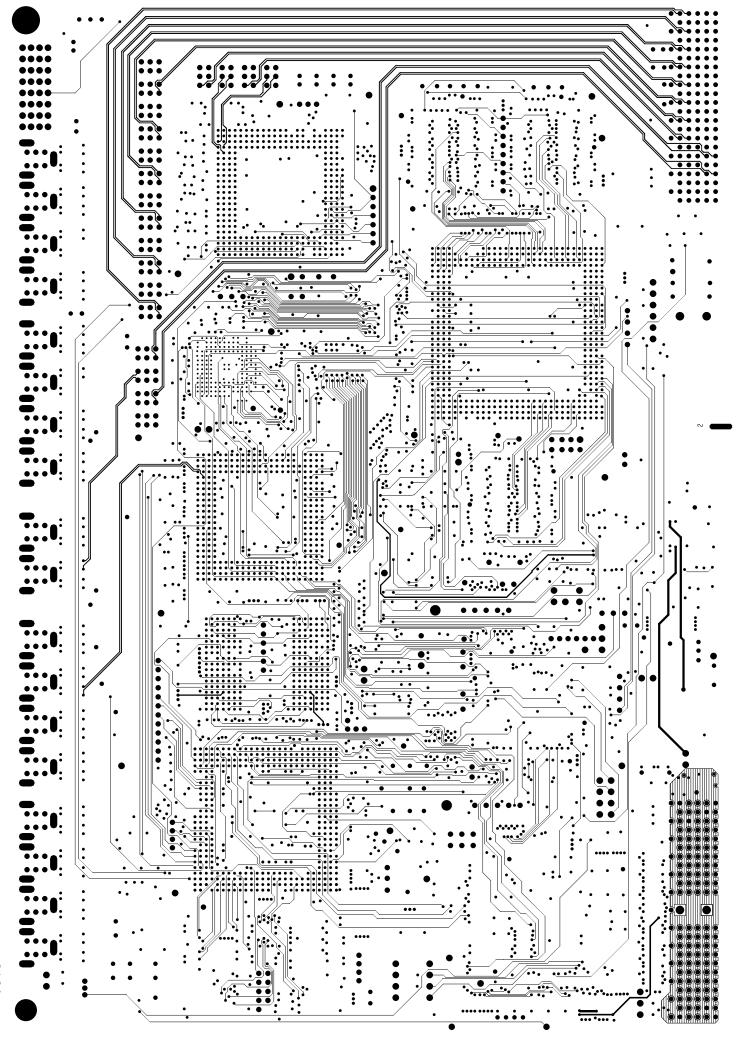

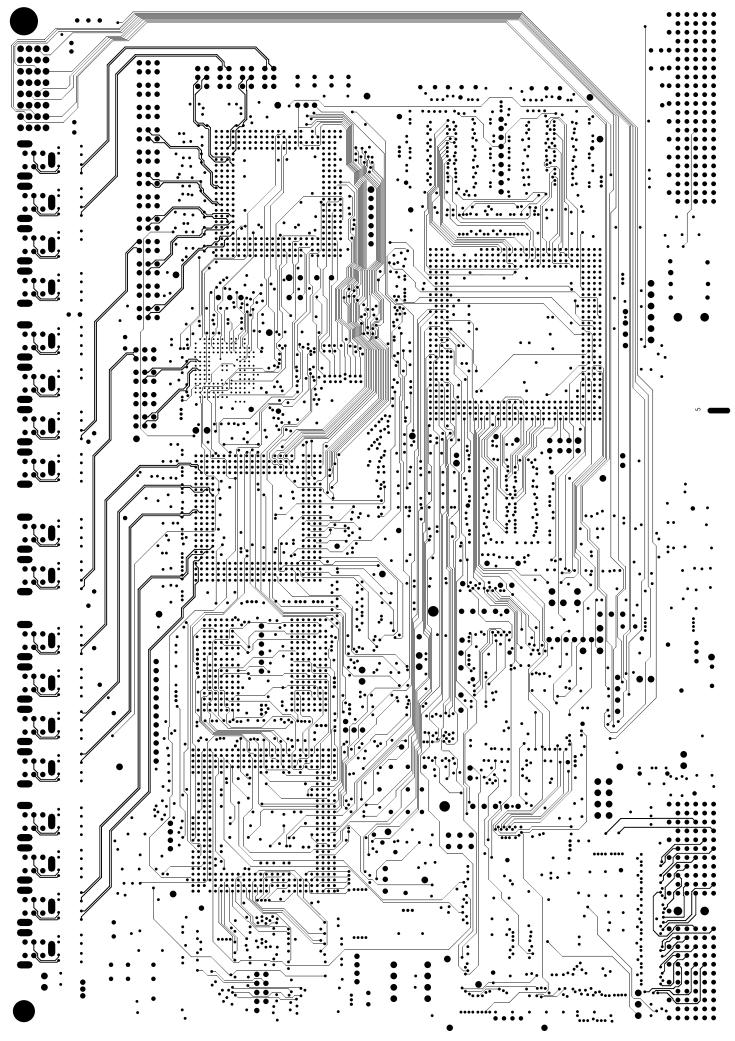

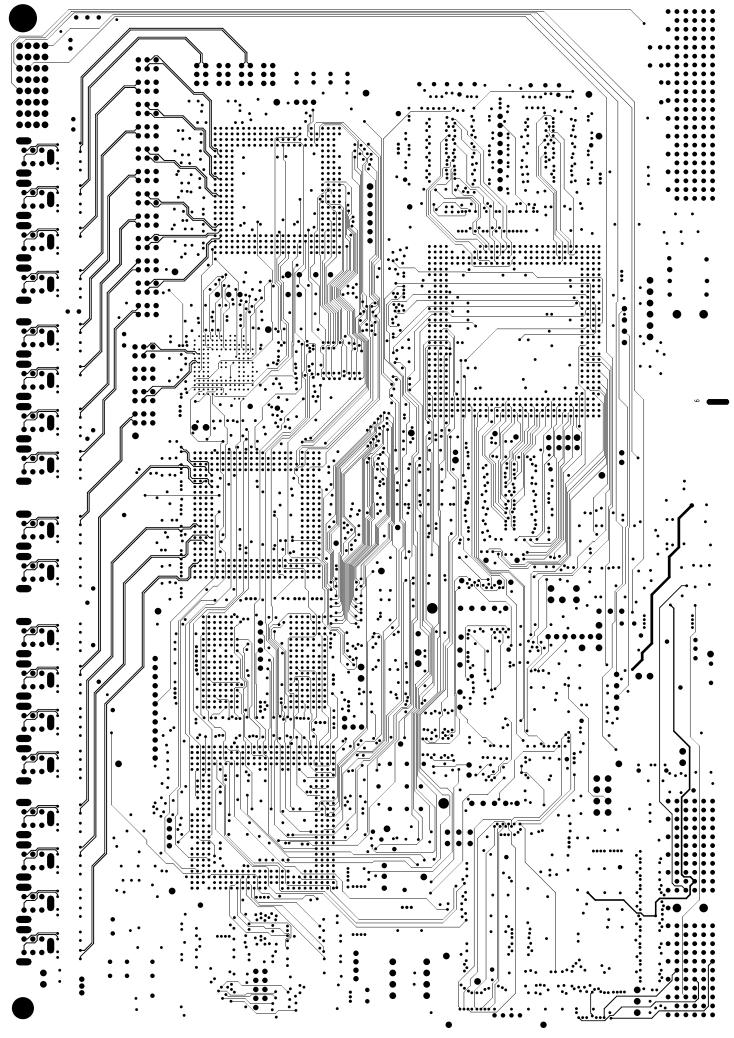

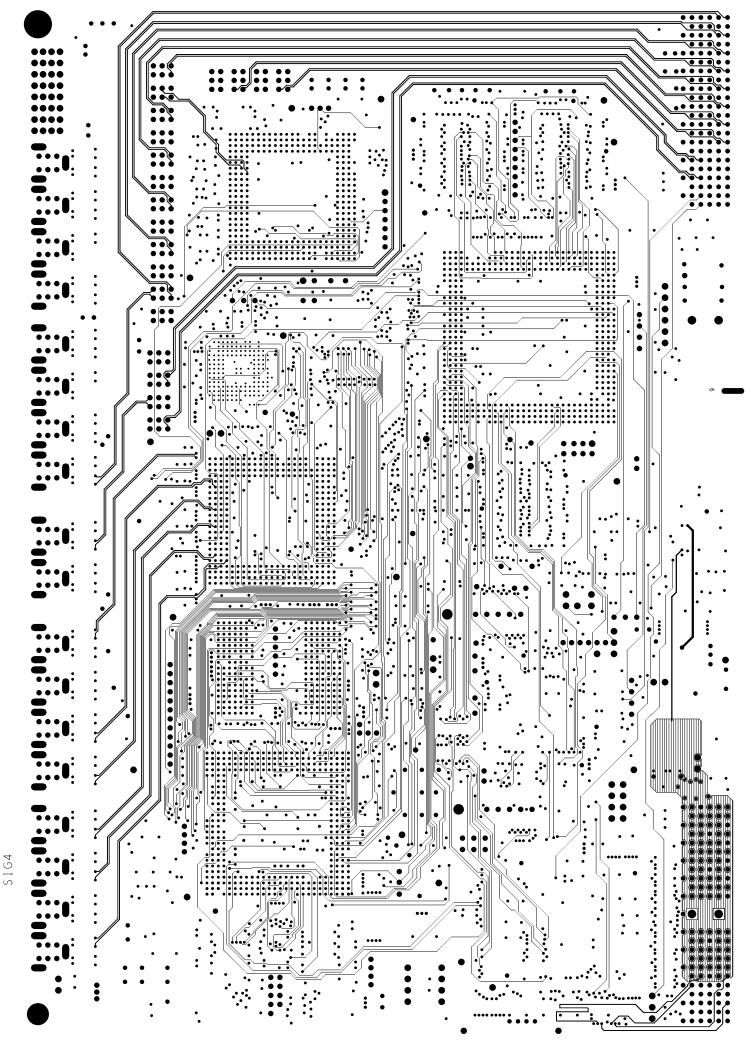

| 21. | APPE  | NDIX H: LAYOUT                                              | 115 |

|     | 21.1. | Drawing Summary Report                                      | 115 |

|     | 21.2. | X-Y Coordinates for Issue 3 Board                           | 116 |

| 22. | APPE  | NDIX I: GLOSSARY                                            | 126 |

PMC-Sierra, Inc.

**VORTEX CHIPSET**

REFERENCE DESIGN PMC-1990815

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

### LIST OF FIGURES

| FIGURE 1.  | DSLAM Reference Design Shelf Architecture                    | 3  |

|------------|--------------------------------------------------------------|----|

| FIGURE 2.  | The Core Card Architecture                                   | 4  |

| FIGURE 3.  | The Core Card Top View                                       | 6  |

| FIGURE 4.  | Core Card Block Diagram                                      | 7  |

| FIGURE 5.  | LVDS on Core Card                                            | 11 |

| FIGURE 6.  | Example of 8kHz Clock Flow on Core Card                      | 13 |

| FIGURE 7.  | Example of Received 8 kHz Time Reference                     | 14 |

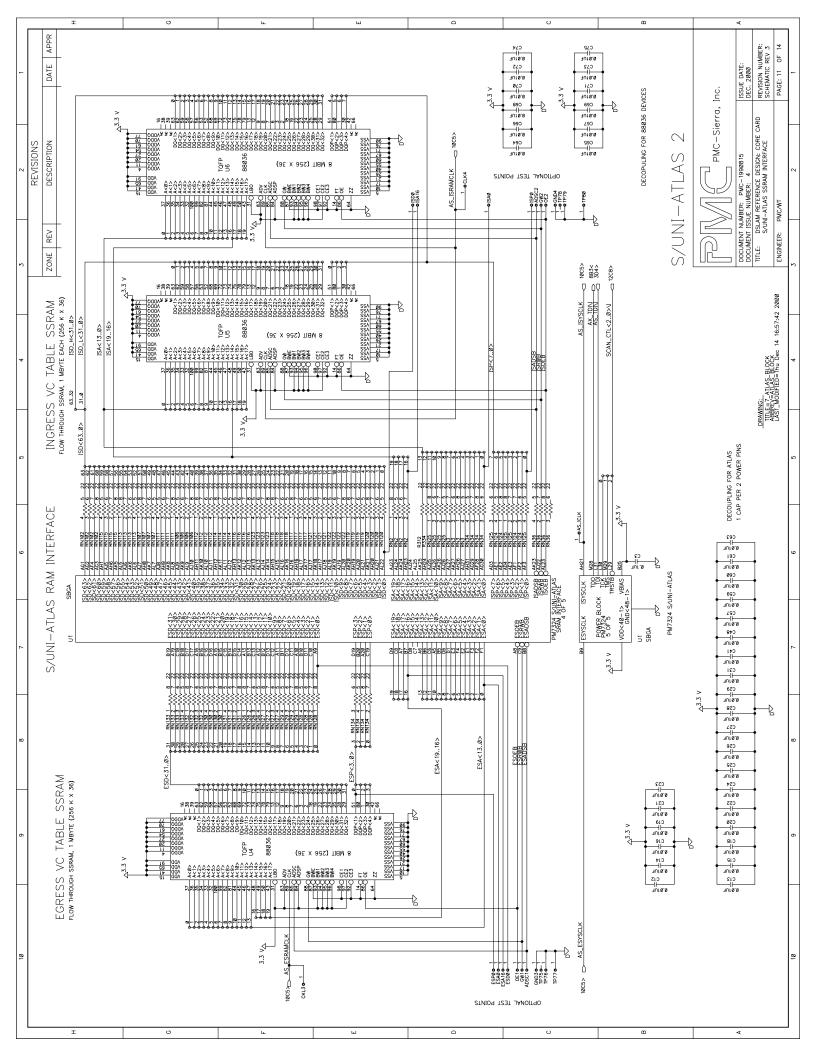

| FIGURE 8.  | S/UNI-ATLAS SRAM VC Table Addressing                         | 16 |

| FIGURE 9.  | VC Ingress S/UNI-ATLAS-SSRAM Connection                      | 17 |

| FIGURE 10. | VC Egress S/UNI-ATLAS-SSRAM Connection                       | 18 |

| FIGURE 11. | Dual Bank Configuration for ZBT SSRAM                        | 24 |

| FIGURE 12. | Single Bank SDRAM 4 MB for 64 k Cells                        | 25 |

| FIGURE 13. | Example of a Hot-Swap Circuit                                | 32 |

| FIGURE 14. | LED_SWITCH\I Line SiganI                                     | 35 |

| FIGURE 15. | cPCI and Local Bus Microprocessor Interface                  | 36 |

| FIGURE 16. | S/UNI-APEX, CPLD, and the Local Bus Microprocessor Interface | 39 |

| FIGURE 17. | CPLD Block Diagram                                           | 50 |

| FIGURE 18. | 8 kHz Interface                                              | 53 |

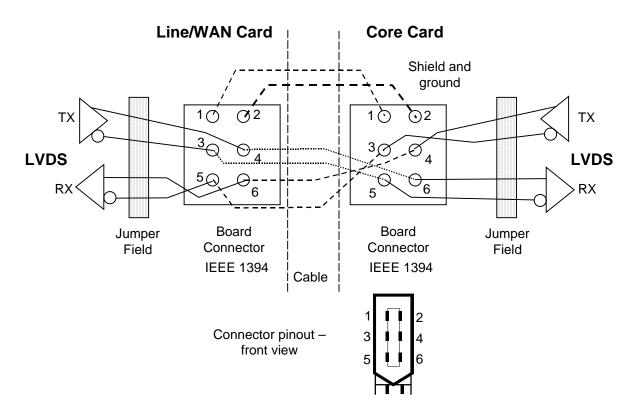

| FIGURE 19. | LVDS Pinout on DSLAM Cards                                   | 55 |

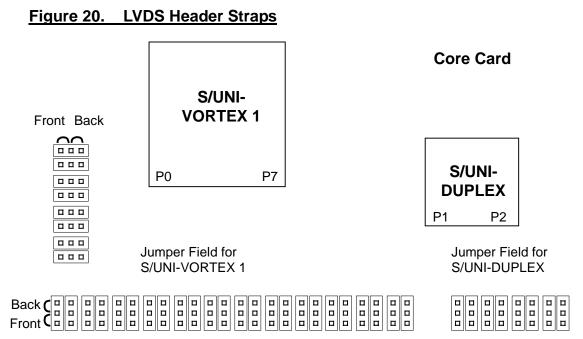

| FIGURE 20. | LVDS Header Straps                                           | 56 |

| FIGURE 21. | Wave Shapes with a Single Active LVDS Transmitter            | 57 |

| FIGURE 22. | LVDS Over Backplane Test Connections                         | 59 |

| FIGURE 23. | LVDS at Core Card and Line Card with LVDS backplane          | 59 |

| FIGURE 24. | Microprocessor Bus Termiantion                               | 61 |

| FIGURE 25. | Examples of Signal Integrity on uP Bus                       | 62 |

| FIGURE 26. | Any-PHY Bus Termiantion                                      | 63 |

| FIGURE 27. | Example of Signal Integrity Downstream at VORTEX-1           | 64 |

| FIGURE 28. | Upstream/Downstream UL2 Bus Termination                      | 65 |

| FIGURE 29. | Example of Signal Integrity Upstream at VORTEX-1             | 66 |

| FIGURE 30. | S/UNI-APEX – S/UNI-ATLAS Bus Termiantion                     | 67 |

PMC-1990815

REFERENCE DESIGN

DSLAM REFERENCE DESIGN: CORE CARD

| FIGURE 31. | RAM Bus Termiantion68                                |

|------------|------------------------------------------------------|

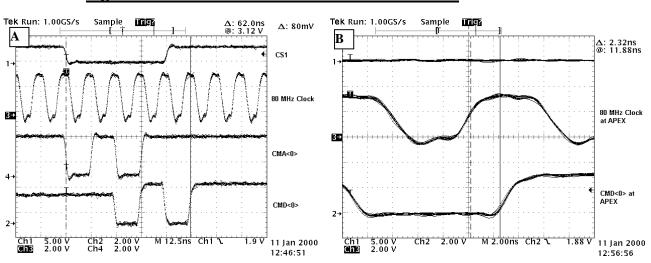

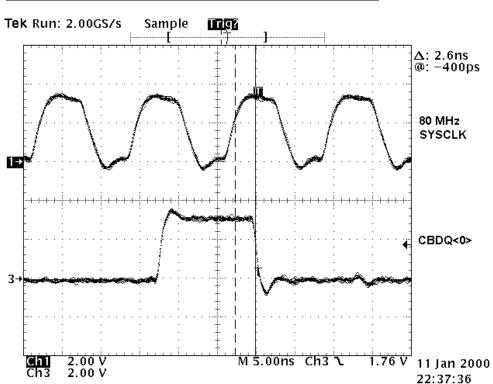

| FIGURE 32. | Waveforms at S/UNI-APEX at 80 MHz69                  |

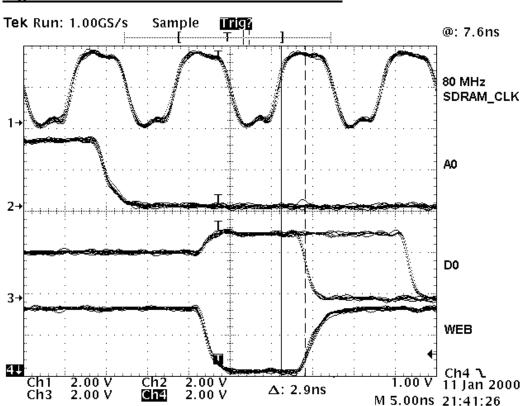

| FIGURE 33. | Waveforms at SDRAM at 80 MHz70                       |

| FIGURE 34. | Waveforms at SDRAM at 80 MHz71                       |

| FIGURE 35. | Waveforms at S/UNI-APEX at 80 MHz72                  |

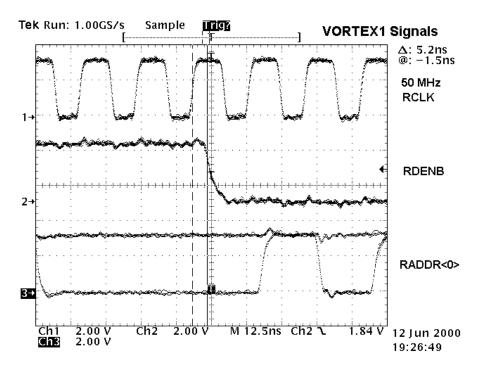

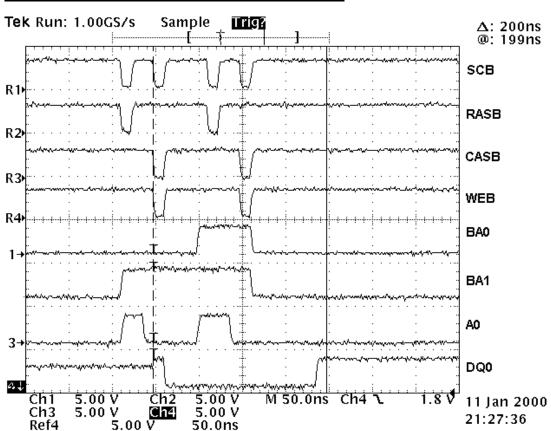

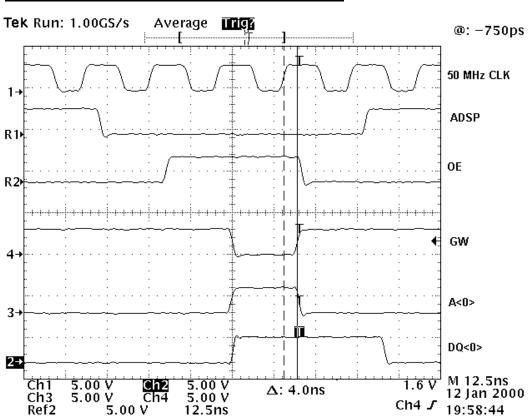

| FIGURE 36. | Waveforms at SSRAM at 50 MHz73                       |

| FIGURE 37. | Front Plate for Core Card74                          |

| FIGURE 38. | Example of LEDs Placement76                          |

| FIGURE 39. | PCB Cross-section                                    |

| FIGURE 40. | Data Path with Internal Loopback                     |

| FIGURE 41. | External Loopback with ATM over DS-3 Tester87        |

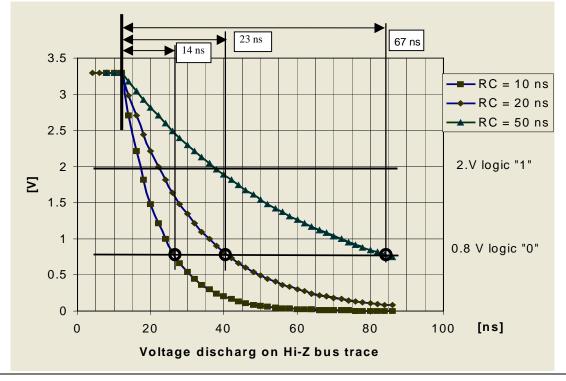

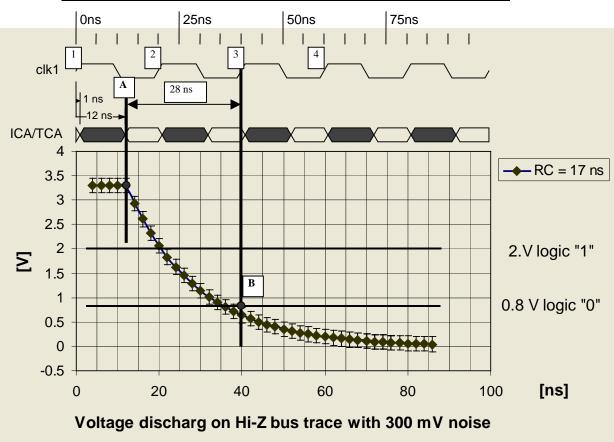

| FIGURE 42. | Voltage Discharge on Hi-Z Bus Line92                 |

| FIGURE 43. | Voltage Discharge on Hi-Z Bus Line with Noise93      |

| FIGURE 44. | Example of SEEP Reading Upon PCI Reset95             |

| FIGURE 45. | Example of SEEP Reading Upon PCI Reset95             |

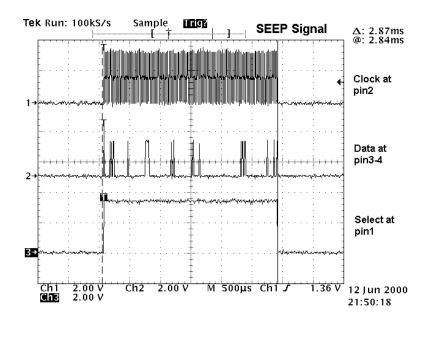

| FIGURE 46. | Example Read from the S/UNI-APEX at 25 MHz96         |

| FIGURE 47. | Example Write to APEX Cycle on Local Bus at 25 MHz97 |

| FIGURE 48. | Example Read from the S/UNI-DUPLEX                   |

| FIGURE 49. | Example Write to the S/UNI-DUPLEX                    |

ISSUE 4

REFERENCE DESIGN PMC-1990815 PMC-Sierra, Inc.

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### REFERENCES

#### PMC-Sierra, Inc. DSLAM Hardware

- 1. PMC-Sierra Inc., PMC-1990832, "DSLAM Reference Design: System Design", Issue 3, September 2000

- 2. PMC-Sierra Inc., PMC-1990354, "DSLAM Reference Design: Line Card", Issue 3, September 2000

- 3. PMC-Sierra Inc., PMC-1990474, "DSLAM Reference Design: WAN Card", Issue 3, September 2000

- 4. PMC-Sierra, Inc., PMC-971154, "Saturn User Network Interface ATM Layer Solution Data Sheet" (S/UNI-ATLAS, PM7324), Issue 7, January 2000.

- 5. PMC-Sierra Inc., PMC-1990816, "DSLAM Apps Note: Signal Integrity and Timing Simulation for the VORTEX Chipset", Issue 1, September 2000

- 6. PMC-Sierra Inc., PMC-1981025, "S/UNI-VORTEX and S/UNI-DUPLEX Technical Overview", Issue 2, June 1999

- 7. PMC-Sierra, Inc., PMC-981224, "ATM/Packet Traffic Manager and Switch Data Sheet" (S/UNI-APEX, PM7326), Issue 6, April 2000.

#### PMC-Sierra, Inc. DSLAM Software

- 8. PMC-Sierra Inc., PMC-1980585, S/UNI -ATLAS Programmer's Guide and Example Software, Issue 2, Feb. 1999

- PMC-Sierra Inc., PMC-1991727, S/UNI-APEX Device Driver Design, Issue 2, May 2000

- 10. PMC-Sierra Inc., PMC-1990786, S/UNI-VORTEX Driver Manual, Issue 1, Aug. 1999

- 11. PMC-Sierra Inc., PMC-1990799, S/UNI-DUPLEX Driver Manual, Issue 1, Aug. 1999

- 12. PMC-Sierra Inc., PMC-1991454, S/UNI-APEX H/W Programmer's Guide, Issue 2, April 2000

- **13.** PMC-Sierra Inc., PMC-1991578, S/UNI-APEX Device Driver Release Notes, Issue 2, June 2000

- 14. PMC-Sierra Inc., PMC-2000781, VORTEX Chipset Driver Release Notes, Issue 1, August 2000.

PMC-Sierra, Inc.

**VORTEX CHIPSET**

ISSUE 4

#### **Industry Standards**

- **15.** Bell Communications Research, "SONET Transport Systems: Common Generic Criteria," GR-253-CORE, Issue 2, December 1995.

- **16.** Bell Communications Research, "Clocks for the Synchronized Network: Common Generic Criteria" GR-1244-CORE, Issue 1, June 1995.

- **17.** ITU-T, "The control of jitter and wander within digital networks which are based on the synchronous digital hierarchy (SDH)", March 1993.

- **18.** PCI Industrial Computers manufacturers Group (PICMG), "CompactPCI Specification", PICMG 2.0 R2.1, September 2, 1997.

- **19.** PCI Industrial Computers manufacturers Group (PICMG), "Hot Swap Specification", PICMG 2.1 R1.0, May 14, 1998. (Draft not approved)

- 20. ADSL Forum, Web Page, http://www.adsl.com

- 21. Montrose, Mark I., "Printed Circuit Board Design Techniques for EMC Compliance", IEEE Press, 1996.

x

PMC-Sierra, Inc.

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### 1. OVERVIEW

The purpose of the Reference Design document set is to assist engineers in designing their products using the PMC-Sierra VORTEX chipset.

The DSLAM Reference Design is composed of these four main documents:

- DSLAM Reference Design: System Design

- DSLAM Reference Design: Core Card

- DSLAM Reference Design: WAN Card

- DSLAM Reference Design: Line Card

The DSLAM Reference Design: System Design document provides an overview of the DSLAM Reference Design system architecture. The remaining documents describe the functionality and implementation specific details for each individual card.

This document specifically describes the design for the DSLAM Core Card. A block diagram illustrates the Core Card design. A description is then given for the functional blocks of the design. A detailed implementation description then follows. The appendixes contains additional information, such as, schematics, bill of material, and CPLD VHDL source.

REFERENCE DESIGN PMC-1990815

DSLAM REFERENCE DESIGN: CORE CARD

#### 2. DSLAM CORE CARD FEATURES

The Digital Subscriber Line Access Multiplexer (DSLAM) Core Card features:

• ATM traffic policing and traffic shaping

**ISSUE 4**

- Small-scale traffic management (switching) with the S/UNI-APEX

- A high-speed Low Voltage Differential Signal (LVDS) interface that:

- Provides data rates up to 200Mb/s

- Allows manual selection of transmission over a backplane or through cables.

- Supports one-to-one (1:1) protection switching

- Support for clock synchronization to either the DS-3 network or the line side interface

- Front panel LEDs to indicate:

- Power supply status

- LVDS signal status

- On-board hot swap controller to monitor the current flow onto the board for live insertion and extraction

- Compact PCI (cPCI) compatibility

DSLAM REFERENCE DESIGN: CORE CARD

#### 3. TYPICAL DSLAM APPLICATION WITH CORE CARD

**ISSUE 4**

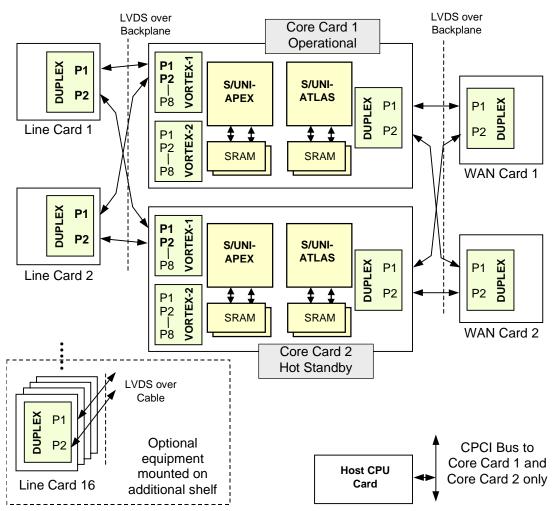

Figure 1 shows a typical application for the S/UNI-DUPLEX, S/UNI-VORTEX, S/UNI-APEX, and the S/UNI-ATLAS.

#### Figure 1. DSLAM Reference Design Shelf Architecture

Figure 1 shows two Core Cards in protective mode. The lower card is the hot stand-bycard that allows one-to-one backup for the operating Core Card.

Also, this block diagram shows a DSLAM development shelf that is equipped with a custom LVDS-backplane, two Line Cards, two WAN Cards, and two Core Cards. A single host CPU card controls Core Cards only. Additional Line Cards can be mounted on a separate shelf with LVDS over cables. Line Cards and WAN Cards, built for the DSLAM Reference Design, have an embedded microprocessor without communication to the cPCI bus.

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### 3.1. Compact PCI (cPCI) Development Shelf

The DSLAM Reference Design for the Core Card is based on a cPCI shelf allowing standardization of interfaces and physical card forms. A custom-made LVDS-backplane is developed demonstrating the LVDS interface functioning over the backplane. LVDS can also be connected with cables through the front plate connectors. The shelf-to-shelf LVDS is implemented using the front plate connectors exclusively. Two Core Cards are used to provide a hot stand-by, as required by the Telcos.

The basic DSLAM development shelf is an 8-slot entity. A 16-slot shelf can be also supported with a single Reference Design Core Card (with an optional hot stand-by card for protection switching).

#### 3.2. DSLAM Reference Design Core Card Architecture

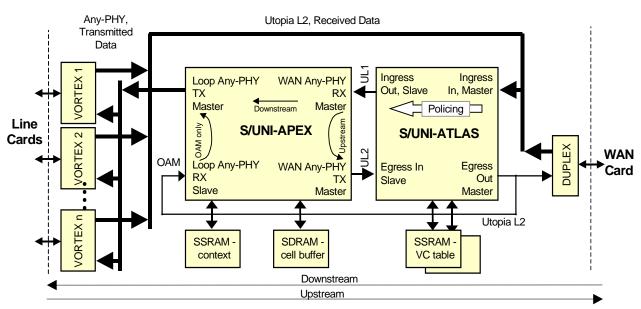

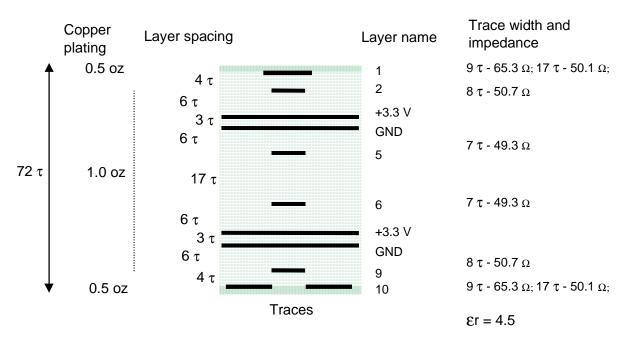

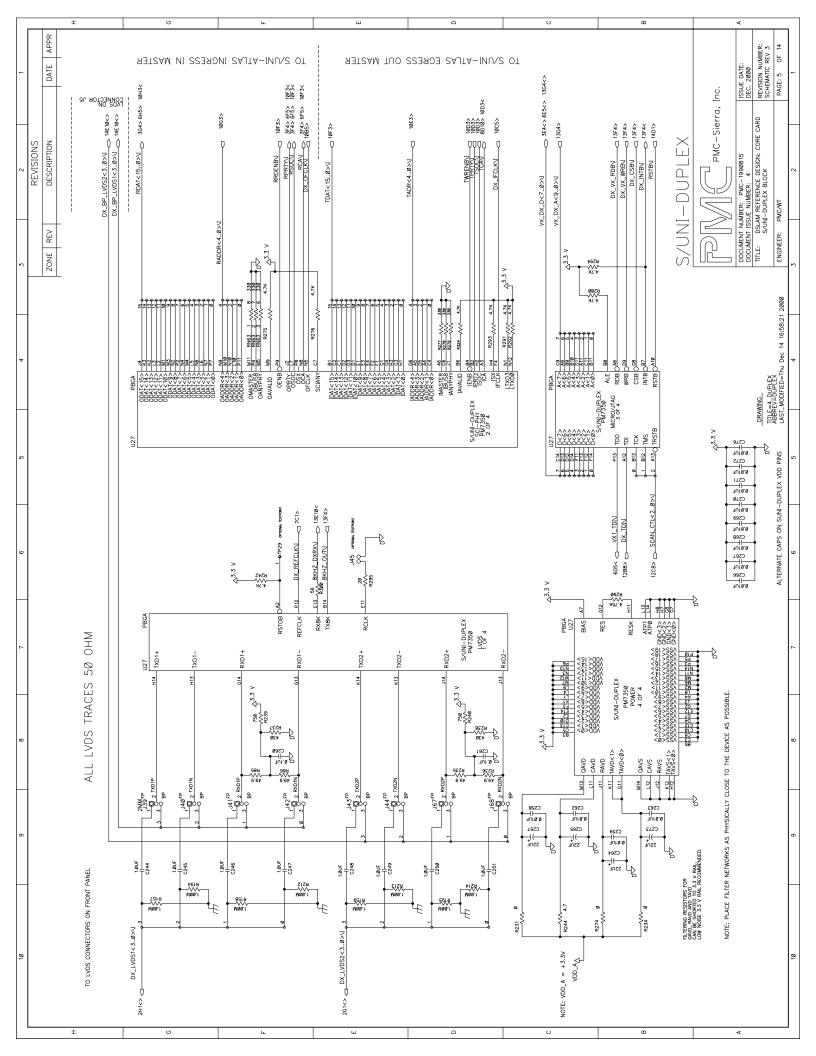

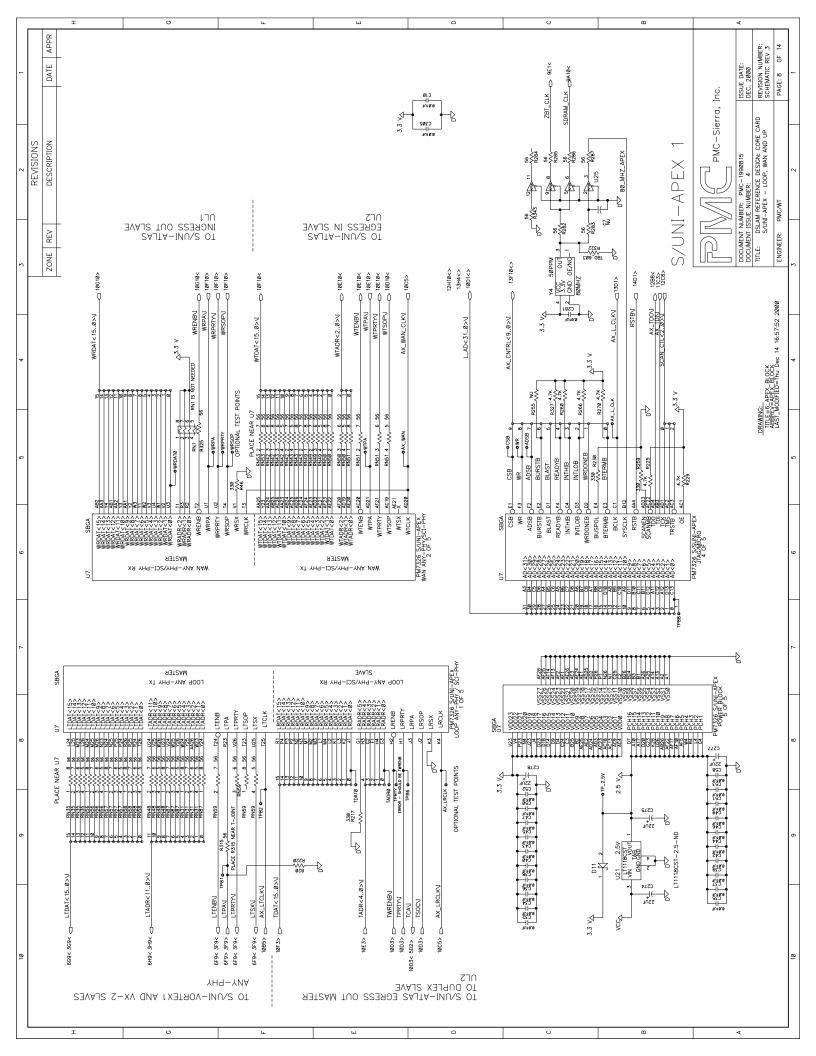

Figure 2 shows the DSLAM Reference Design and Core Card Reference Design that is built around a single S/UNI-ATLAS architecture.

#### Figure 2. The Core Card Architecture

The S/UNI-APEX and S/UNI-ATLAS are the core of the design. The downstream and upstream cells are interfaced to the S/UNI-ATLAS through the same *Ingress In, Master*port. The *Loop Any-PHY RX, Slave* port on the S/UNI-APEX is connected to WAN direction *Egress Out, Master* allowing OAM cell flow (RDI from the S/UNI-ATLAS towards downstream). The S/UNI-APEX switches cells to *Loop Any-PHY TX, Master* or to *WAN Any-PHY TX, Master* ports as required per

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

cell destination. The Core Card interface to the Line Cards is through a set of S/UNI-VORTEX devices. The Core Card interface to the network is through the S/UNI-DUPLEX, which provides an LVDS link to the WAN Card.

In the upstream direction, the S/UNI-ATLAS takes cells from the Line Cards and performs a look-up, based on the PHY number, VPI, and VCI that are used to identify the associated connection. Once the connection is identified, the cell is processed according to the configuration of the connection. In this application, the S/UNI-ATLAS performs the header translation, <u>per-PHY and per-VC</u> policing, performance monitoring, and fault management. Prepend and postpend are used to navigate the cell.

In the downstream direction, the S/UNI-ATLAS accepts the cells coming from a WAN Card and a direct look-up is performed to identify the connection. The cell is then processed according to the configuration in the context table for that connection (cell is tagged). The header translation and OAM processing can be done at the ingress. The tagged cell is sent to the S/UNI-APEX *WAN Any-PHY RX, Master* port. The S/UNI-APEX puts the cell into a queue and sends it to either *Loop Any-PHY TX, Master* or *WAN Any-PHY TX, Master* ports. The tag determines the port. If the cell destination is loop side, then the cell goes through the *Loop Any-PHY TX, Master* port to one of the S/UNI-VORTEX multiplexers, where the destination channel matches the tag number. The cell is passed to one of 32 queues for transmission by the appropriate PHY.

The AIS cell coming from the loop (upstream) arrives at the S/UNI-ATLAS *Ingress In* port. The S/UNI-ATLAS generates the RDI cell with the tag that corresponds to the port where the AIS cell arrived. The RDI cell is sent to the *Egress Out* port and then arrives at the S/UNI-APEX slave port, *Loop Any\_PHY RX*, only if the tag matches the loop side destination. The S/UNI-APEX puts the RDI cell into a queue and sends the cell through the *Loop Any-PHY TX, Master* port to one of the S/UNI-VORTEX multiplexers, where the destination channel matches the tag number.

The network management entity has to assign unique port (channel) numbers to all S/UNI-DUPLEX and S/UNI-VORTEX devices attached to the Utopia L2 bus.

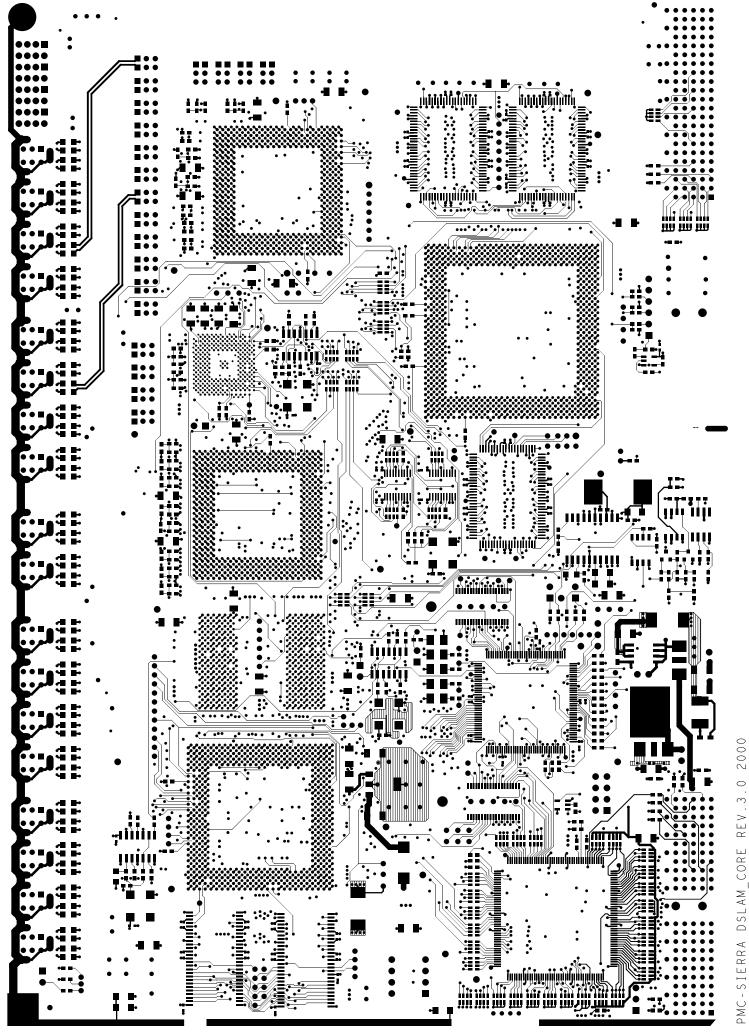

The Core Card picture is shown in Figure 3 below.

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

### Figure 3. Core Card Top View

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### 4. CORE CARD FUNCTIONAL EXPLANATION

#### 4.1. Core Card Block Diagram

This section briefly describes the Core Card block diagram.

#### 4.1.1. Block Diagram Drawing

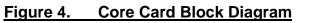

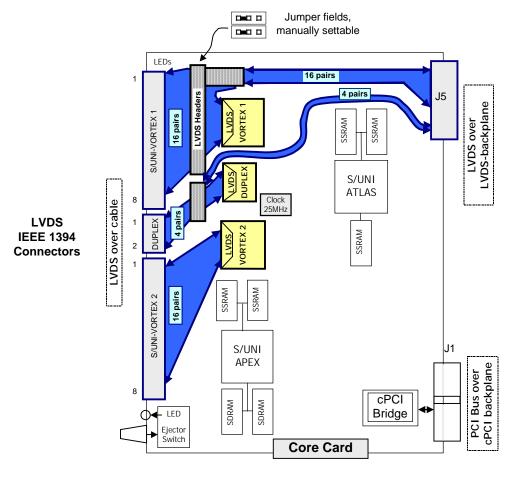

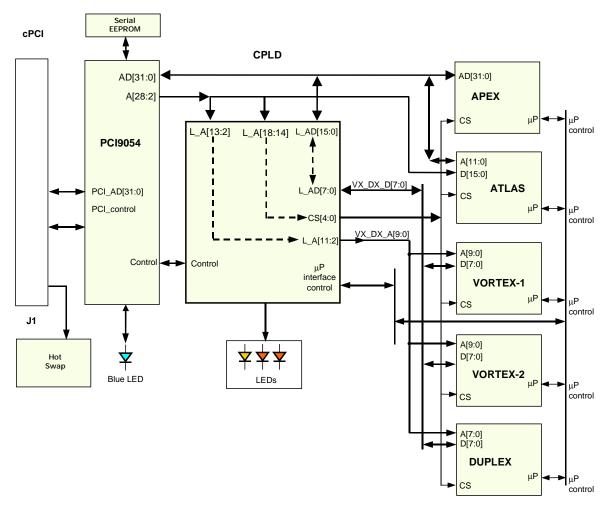

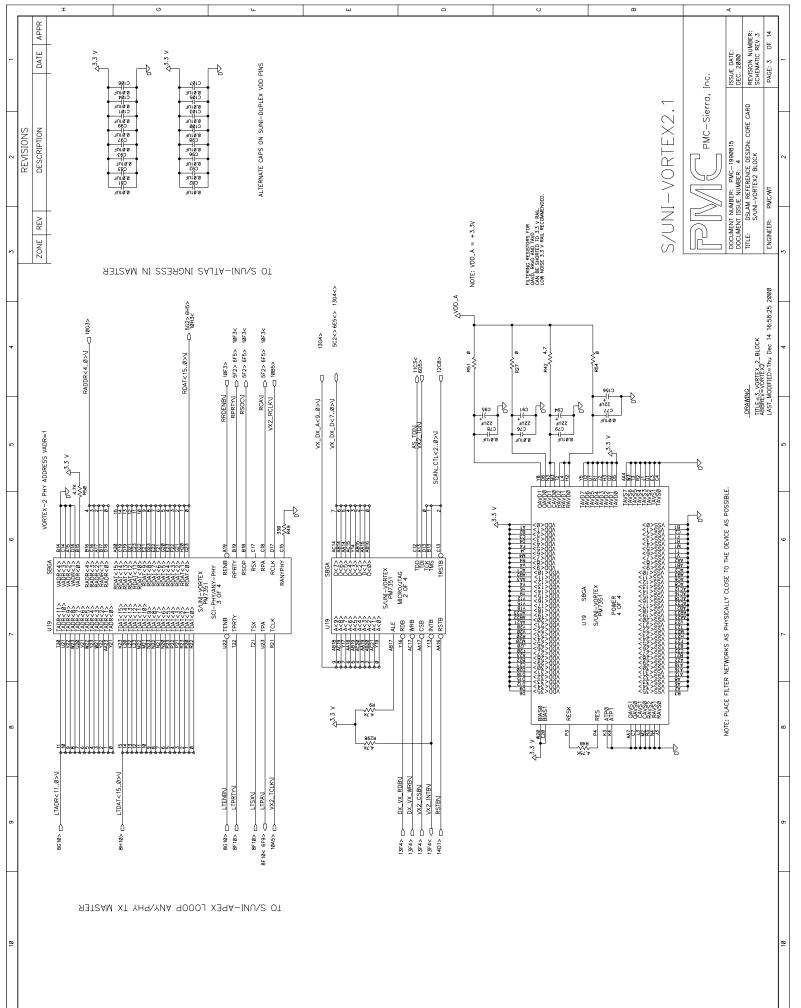

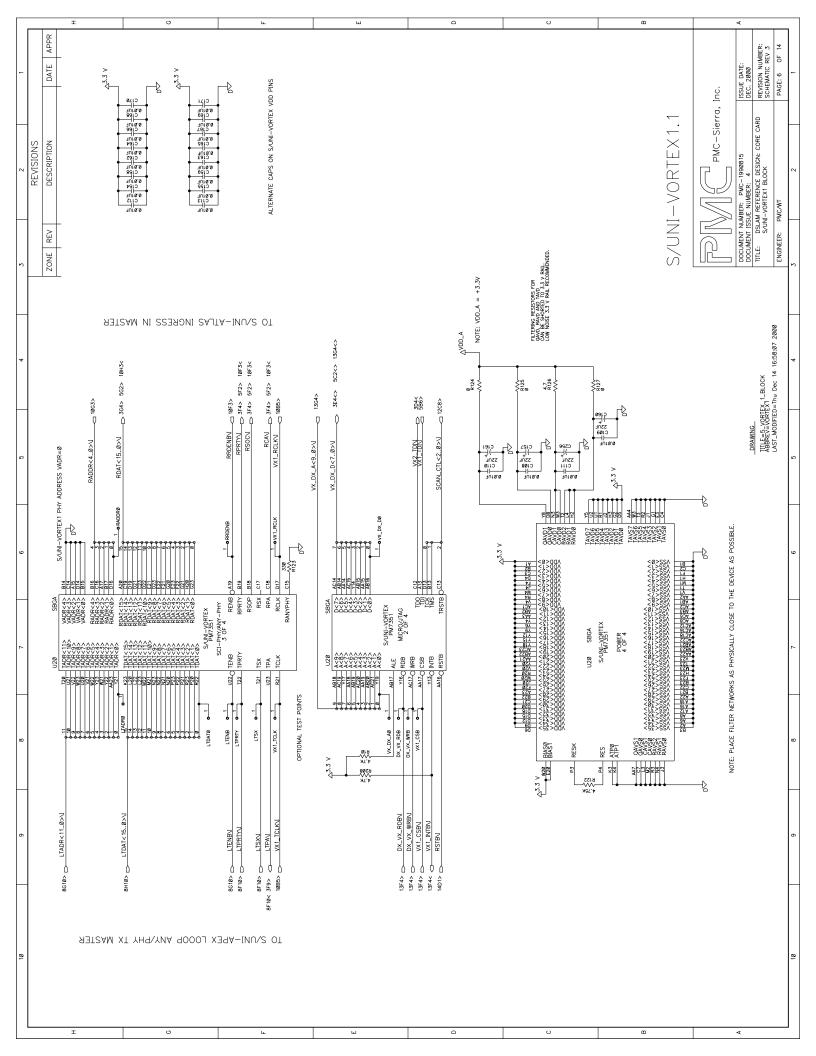

Figure 4 shows the Core Card layout block diagram.

The block diagram shows the PMC Sierra chipset associating with RAMs, clocks, PCI bridge, and CPLD. LVDS connectors at the front and at the back of the Core Card allow an interface to the high-speed LVDS signals (up to 200 Mbps). The PCI bus and power (+5 V and +3.3 V) are connected through J1. A system synchronization 8 kHz clock (stratum clock) can be interfaced at the internal headers.

PMC-1990815

**ISSUE 4**

**VORTEX CHIPSET**

REFERENCE DESIGN

DSLAM REFERENCE DESIGN: CORE CARD

#### 4.1.2. VORTEX Chipset

Five chips shown in the block diagram above create a single entity called VORTEX chipset, including the S/UNI-ATLAS, S/UNI-APEX, S/UNI-DUPLEX, and S/UNI-VORTEX. The VORTEX chipset, and Core Card as well, provides ATM traffic policing (S/UNI-ATLAS), ATM cell traffic management (S/UNI-APEX), and ATM cell multiplexing (S/UNI-VORTEX and S/UNI-DUPLEX).

In the downstream direction, the S/UNI-APEX sends data to the S/UNI-VORTEX and then to the Line Card(s) through the PMC-Sierra Any-PHY interface. The Any-PHY interface supports a bandwidth of up to 800 Mb/s and allows for 2048 channel addressing. The data format is an ATM cell with a prepended single address word.

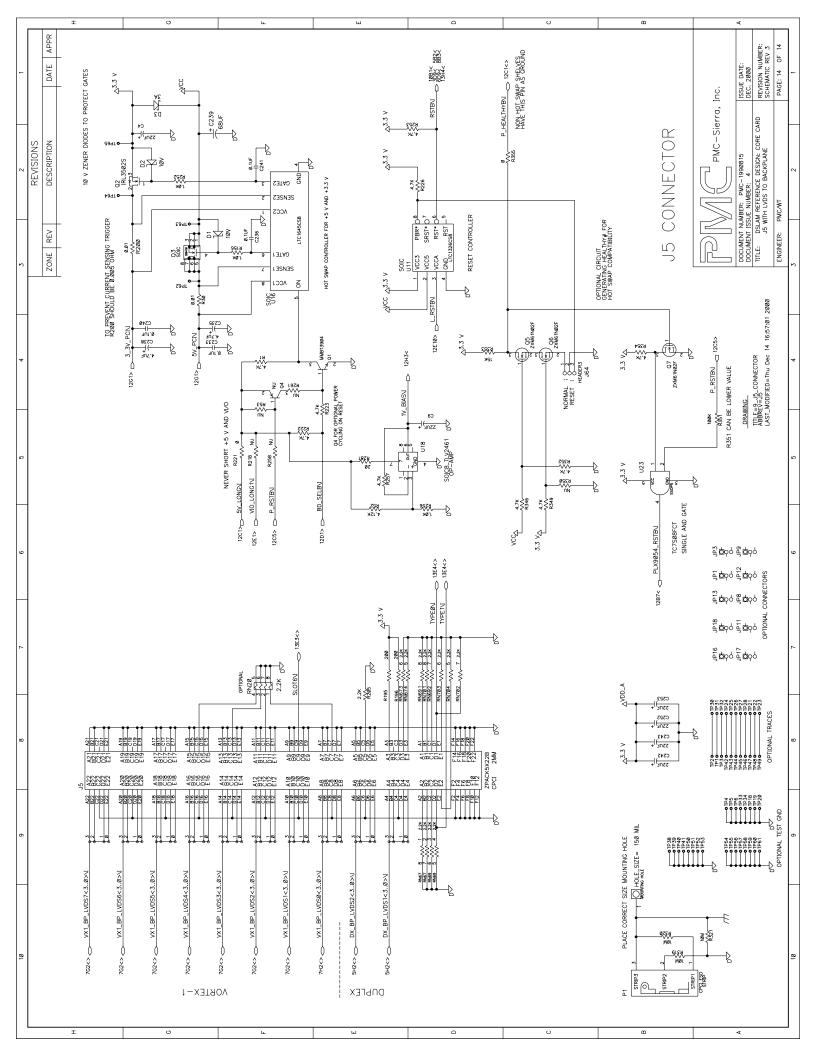

On the user (loop) side, the Core Card provides an interface through the S/UNI-VORTEX-1 or S/UNI-VORTEX-2 to the Line Cards. On the network side, the Core Card provides an interface through a S/UNI-DUPLEX to the WAN Card. Both interfaces are LVDS type with data transfer rates up to 200 Mb/s.

The S/UNI-ATLAS provides traffic policing and OAM functionality. A single entry port to the S/UNI-ATLAS of both upstream and downstream cells (specific to this Reference Design) provides easy traffic policing - the S/UNI-ATLAS implements that function in the Ingress direction only.

The VORTEX chipset is described in more details later in this document.

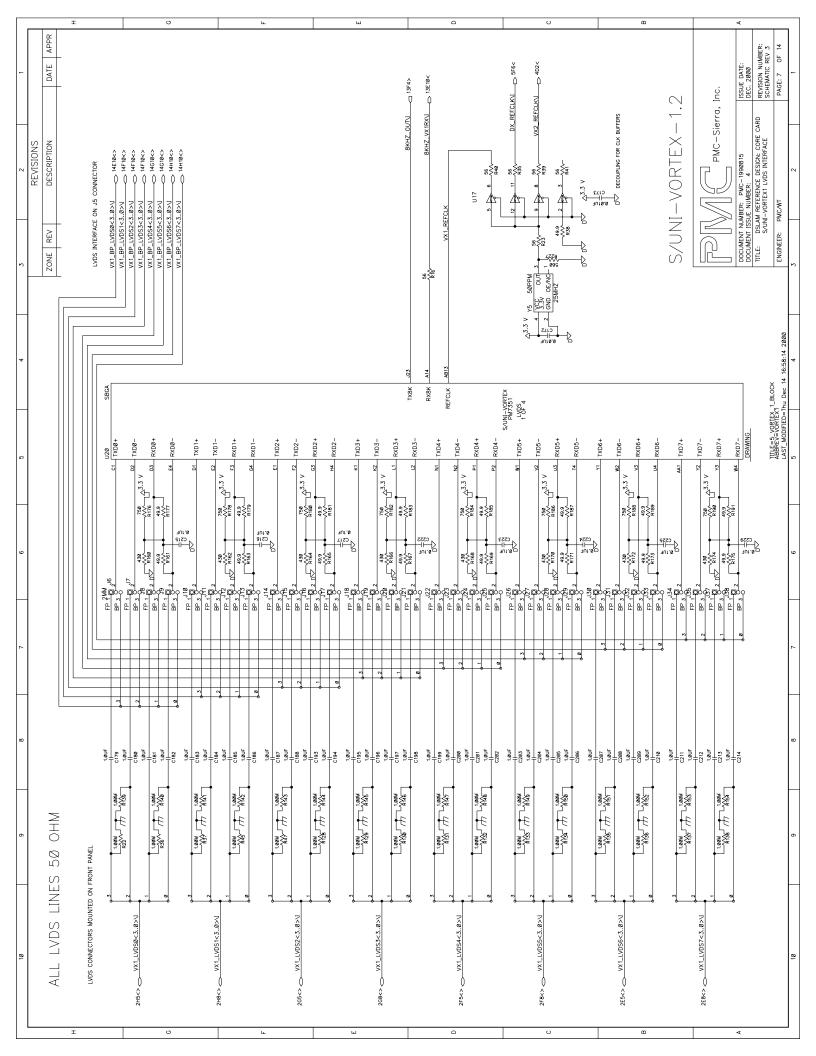

#### 4.1.3. LVDS Interface

The Core Card provides an interface for the LVDS from the front plate or from the LVDS-backplane. The LVDS interface at the front panel allows access to eight ports on the S/UNI-VORTEX-1, eight ports on the S/UNI-VORTEX-2, and two ports on the S/UNI-DUPLEX. LVDS over the backplane provides an interface to eight ports on the S/UNI-VORTEX-1 and two ports on the S/UNI-DUPLEX. Space limitations prevent all LVDS ports of the S/UNI-VORTEX-2 from being accessible at the back connector J5. The LVDS connectors were chosen to be an IEEE Firewire type that supports a data rate in excess of 200 Mb/s.

The LVDS drivers, receivers, copper traces, and connectors are designed to work in 50/100 ohm environment. Individual trace and driver is designed for 50 ohm characteristic impedance. The differential LVDS lines at the receiver inputs are loaded with external 100 ohm resistors.

More on LVDS can be found in sections 4.2, 9.2, 9.3 and 10 in this document.

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

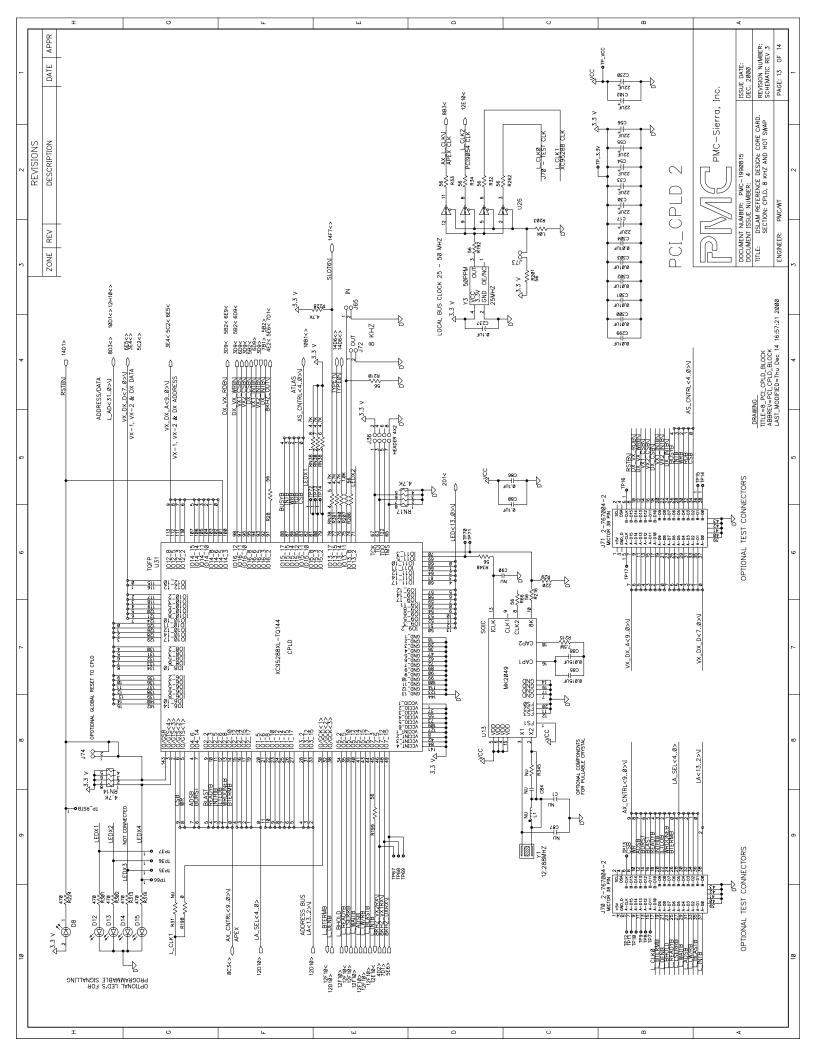

#### 4.1.4. PCI Bridge

The Core Card does not have an on-board microprocessor. The PCI bus host processor card provides an interface to the Core Card through a cPCI bridge device, which only uses a read/write (burst) register sequence and interrupt service. The cPCI bus does not carry payload data, which enables the host CPU to maintain all DSLAM cards through the cPCI bus without burden of ATM traffic over cPCI. If required, cells can be inserted into traffic through the cPCI interface.

The hot swap compatible PCI bridge (PLX PCI9054) is used as the PCI bus interface. The bridge operates in multiplexed mode on the local bus side. The PCI9054 provides an interface to a CPLD for address decoding (chip enable).

The local bus speed is set at 25 MHz, which allows the microprocessor interface on all devices to run at the optimum speed.

The PCI9054 requires a serial EEPROM (SEEP) to boot on power-up (or reset).

#### 4.1.5. Hot Swap Controller

The hot swap controller LTC1645, and discrete components are used to make the Core Card hot swap compatible. This device is accompanied with the LTC1326 supply voltage monitor and reset line generator.

#### 4.1.6. Ejector Handle and LED

The ejector handle has a built-in microswitch that toggles when the ejector changes position. The activity is detected by the cPCI bridge, which in turn notifies the host CPU about the status change. A blue LED signals the card's "not-ready-yet" status upon insertion or the card's readiness for removal. NOTE: This functionality requires specific software driver, which is not supported by the PMC-Sierra VORTEX Chipset Driver. Also, the host CPU card must have hardware provision to detect activities on the ENUM# line.

#### 4.1.7. CPLD

A CMOS Programmable Logic Device (CPLD) is used to provide address decoding, LED latches, interrupt latches, and 8 kHz clock routing. The Xilinx XC95144 was chosen for this design.

The CPLD is in-circuit programmable through a header connector.

PMC-Sierra, Inc.

**ISSUE 4**

**VORTEX CHIPSET**

DSLAM REFERENCE DESIGN: CORE CARD

#### 4.1.8. RAMs

The S/UNI-ATLAS and the S/UNI-APEX need fast RAMs to buffer large amounts of data.

The S/UNI-APEX needs both SDRAM and SSRAM. Both RAMs operate at 80 MHz. The Reference Design shows oversized RAMs due to chip availability and system verification purposes. The Core Card cell throughput can be supported with smaller RAM sizes. The cell buffer SDRAMs are at 16 MBytes in two integrated circuits. The context memory NBT (ZBT) SSRAM is shown as 4 MBytes that use two integrated circuits. Also, RAM size depends on availability of RAM chips at the time the Core Cards are assembled.

The S/UNI-ATLAS needs two sets of RAM for VC\* look-up tables on Ingress and Egress directions. Those RAMs are SSRAMs working at 50 MHz. The Reference Design for S/UNI-ATLAS is supported with enough SRAM for 16 k connections at the Ingress and Egress. The Egress uses one 128 k x 36 SRAM (36-bit wide data bus). The Ingress uses one bank of two 128 k x 36 SRAMs to make up the 72 bit wide data bus. The S/UNI-ATLAS must interface with synchronous flow-through SRAMs (non-pipelined).

\*/ VC – Virtual Connection. This refers either to Virtual Path Connection (VPC) or Virtual Channel Connection (VCC) within a physical link.

PMC-1990815

REFERENCE DESIGN

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### 4.2. DSLAM High-Speed LVDS Serial Interface

The S/UNI-DUPLEX and S/UNI-VORTEX provide backplane interconnection through 100 to 200 Mb/s serial LVDS links. All cells flown to and from Core Card, and cells processed on the Core Card are concentrated on these high-speed links. Clock is not transmitted to avoid clock skew issues, and the receiver recovers the clock from the incoming data.

For more information on the high-speed LVDS link, see DSLAM system design document [1].

#### 4.2.1. Example of LVDS Routing on Core Card

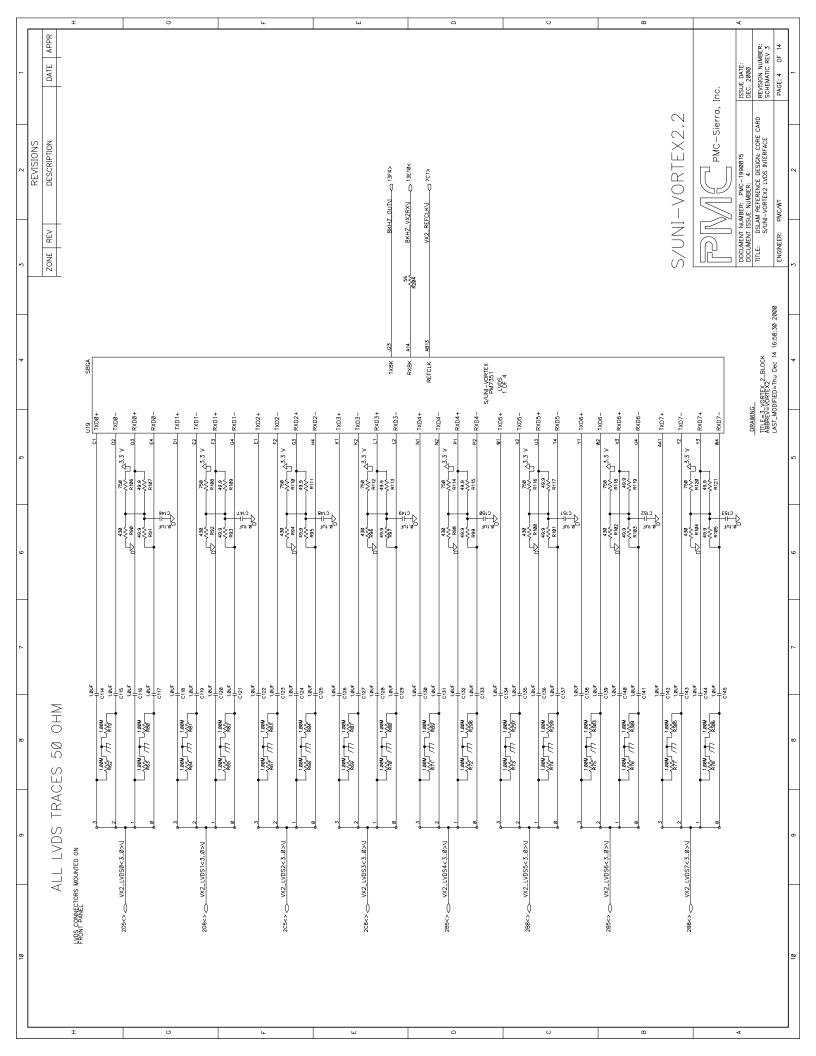

The Core Card provides an LVDS interface to both the LVDS-backplane and to the front panel. Block diagram, shown in Figure 5, highlights components that support LVDS on the Core Card.

#### Figure 5. LVDS on Core Card

**VORTEX CHIPSET**

DSLAM REFERENCE DESIGN: CORE CARD

Manually settable header fields are used to direct LVDS flow. The setup must be done before the card is inserted into the DSLAM shelf.

S/UNI-VORTEX-1 and the S/UNI-DUPLEX can provide an interface to J5 or to the front panel. S/UNI-VORTEX-2 provides an interface to the front panel only. The total number of LVDS traces to J5 (and running on the LVDS-backplane) is 40. This large number of high-speed connections may create crosstalk on the cPCI connector. Separating "hot" lines with ground pins can minimize this crosstalk.

The LVDS traces to the front plate connectors are relatively long. Care must be taken to avoid crosstalk to/from digital lines. The front panel connectors are the FireWire type (IEEE 1394), designed to handle differential signals up to 400Mb/s. Other low cost solutions, such as UTP-5 RJ-45 type connectors, are physically too wide to support eighteen ports.

#### 4.2.2. LVDS Transmitters vs. Hot Swap

The LVDS interface is fully hot swap compatible. The LVDS transmitters can stay active or can be turn off (disabled) on live cards, while another card is hot plugged in. For example, the transmitter disable function is executed on the S/UNI-DUPLEX by writing register 0x05 with value 0x30. The S/UNI-VORTEX registers 0x095, 0x0B5, 0x0D5, 0x0F5, 0x115, 0x135, 0x155 and 0x175 disable LVDS transmitter per HSS link by writing 0x08. After inserted card is operable, writing *zero* to appropriate bits in corresponding registers can activate the transmitters.

<u>IMPORTANT</u>: Proper register write sequence is required to ensure cell transfer over the LVDS interface and Utopia bus. The sequence is implemented in the VORTEX Chipset driver files vcs\_api1.c and dpx.c. It is important to make sure the S/UNI-DUPLEX OCAEN bit in register 0x0A stays disabled until S/UNI-ATLAS polling is enabled. The OCAEN is set to 1 at the very last write, enabling cell transfer from the S/UNI-DUPLEX at that interface. The above sequence applies to the card that is initialized after power up and also to any card that has interface setup changed. Software designers are required to observe sequencing in their drivers.

More on LVDS can be found in sections 9.2, 9.3 and 10 in this document.

#### 4.3. 8kHz Interface

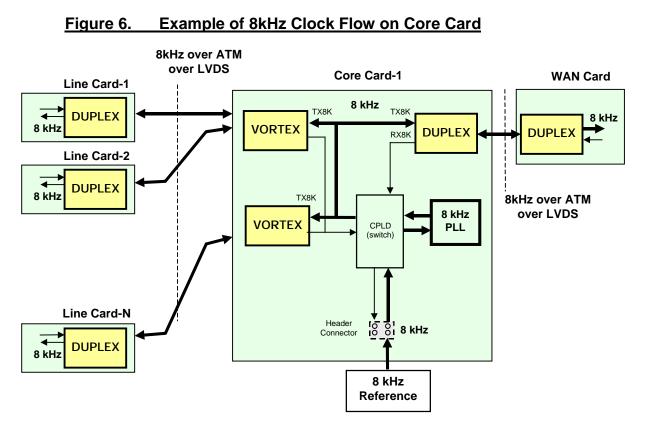

The S/UNI-DUPLEX and the S/UNI-VORTEX provide a mechanism for transporting an 8 kHz time stamp over the LVDS connection. This 8 kHz signal is

used to synchronize the whole network with a single reference clock. Figure 6 shows an example of the 8 kHz DSLAM network synchronization.

The 8 kHz signal is entered and received to/from the S/UNI-VORTEX or S/UNI-DUPLEX at the dedicated pins TX8K or RX8K. The time reference is encoded in the third byte of the prepend attached to a modified ATM cell transmitted over the serial high-speed LVDS connection.

A brief description of the circuit is as follows. The 8 kHz clock can be fed to the system at different points – through the Core Card, WAN Card, or Line Cards. The highlighted flow shows 8 kHz distributed from the Core Card. The 8 kHz time stamp is encoded in cells sent by the S/UNI-VORTEX and S/UNI-DUPLEX on the Core Card and then to the S/UNI-DUPLEX on the Line Card and WAN Card. The WAN Card filters out encoding jitter through the 8 kHz PLL, before it is used for further synchronization. The DSLAM Reference Design Line Card can derive 8 kHz time stamp and feed into the Comets. The Comet has an internal 8 kHz dejittering circuit; therefore, cards have no additional 8 kHz PLL.

The Core Card 8 kHz path is controlled through the cPCI bridge and a CPLD.

The received 8 kHz clock on the S/UNI-VORTEX / S/UNI-DUPLEX pin RX8K is a pulse that lasts 16 clock cycles on the clock at the LVDS connection. If LVDS is at 200 MHz, then the pulse is 16 x 5 ns = 80 ns long and repeats at 125 us (8 kHz).

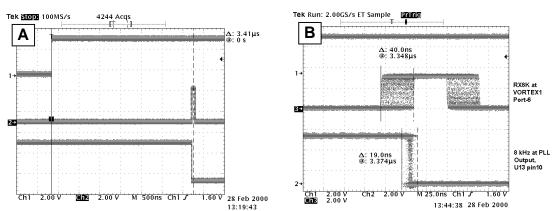

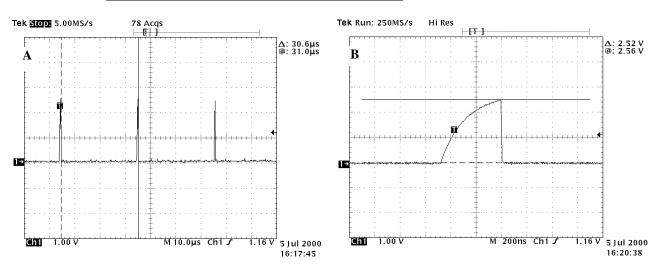

Figure 7 shows an example of an oscilloscope captured time reference that has been recovered on the Core Card.

#### Example of Received 8 kHz Time Reference Figure 7.

RELEASED

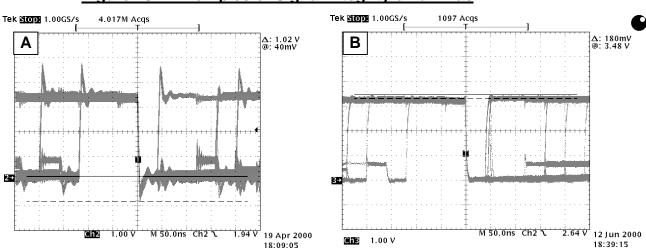

PMC-1990815

Graph A shows the edge of the 8 kHz reference clock inserted to the S/UNI-VORTEX, received time reference pulse at the S/UNI-DUPLEX RX8K output pin, and resynchronized 8 kHz clock at the PLL output.

Graph B shows jitter on the received time reference pulse and edge of the 8 kHz square wave at the PLL output. Attenuated edge jitter is approximately 19 ns, which can be converted to approximately 0.00015 UI peak-to-peak.

For more information about the DSLAM 8 kHz clock distribution, see the DSLAM system design document [1].

Protection switching, executed in our lab, showed no adverse affect on the 8 kHz clock phase and frequency synchronization. For more information about network synchronization and phase-frequency shift, see the DSLAM system design document [1] and also in [9], [16], and [17].

REFERENCE DESIGN PMC-1990815

ISSUE 4

#### 5. CORE CARD CHIPSET OVERVIEW

This section briefly describes the DSLAM chipset.

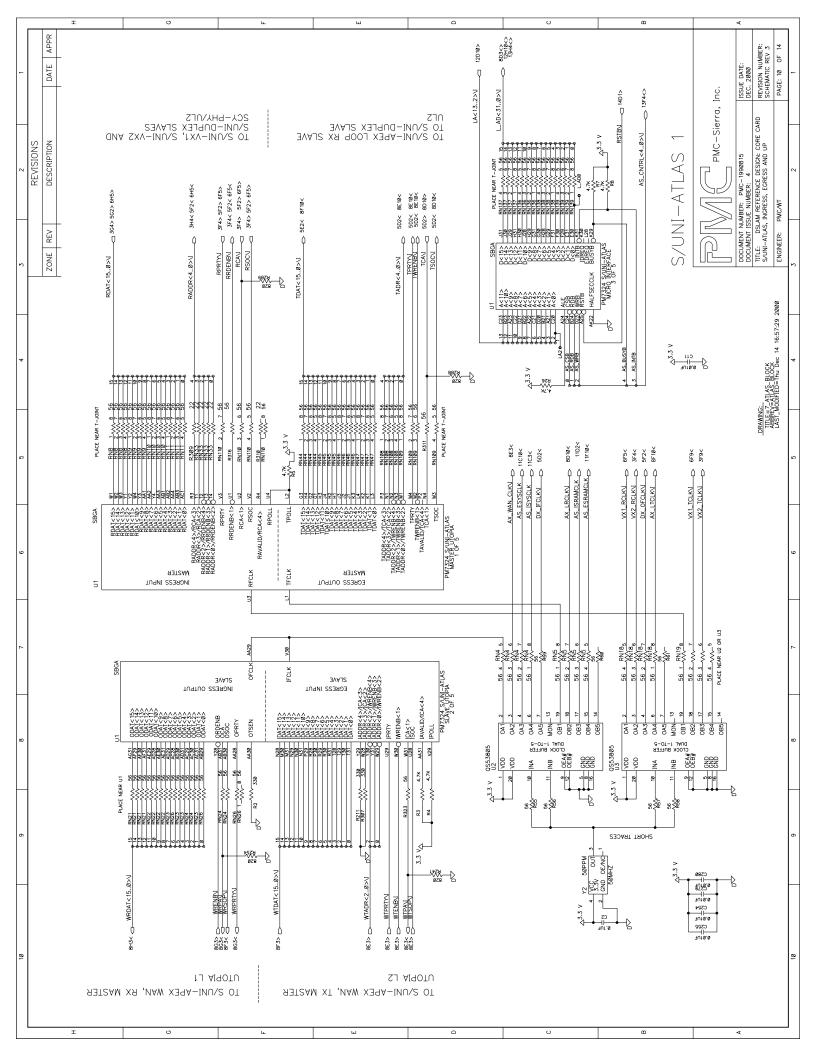

#### 5.1. PM7324 S/UNI-ATLAS

The S/UNI-ATLAS is the PMC-Sierra standard product that implements the following ATM Layer functions:

- OAM processing, according to the ITU-T I.610 1995 and 1998 living list.

- Header Translation on full VPI/VCI address range.

- Prepend and postpend tagging.

- Cell rate policing according to ITU-T I.371 using the Generic Cell Rate Algorithm.

- GFR Policing according to ATM Forum's Traffic Management 4.0 1998 living list.

- Per-PHY queuing to prevent head-of-line blocking.

The S/UNI-ATLAS performs both ingress and egress functionality. The ingress side has a SCI-PHY level 2 (Utopia L2) interface at the input, and a SCI-PHY level 1 (Utopia L1) interface at the output. Cells coming into the S/UNI-ATLAS from a PHY are identified according to the PHY ID, VPI, and VCI using a binary search process. The cells are processed according to the information stored in context RAM for the particular connection. Cells may also be copied to the microprocessor cell interface for external processing.

The egress port has a SCI-PHY level 2 interface at both the input and output interface. The connection is identified (using a direct lookup process) by the PHY ID, VPI, and VCI, and processed according to the information in external RAM for the particular connection. Like the ingress port, cells can be copied to the microprocessor cell interface for external processing. The software, VORTEX Chipset Driver that controls the Reference Design Core Card, sets the cell header remapping in the S/UNI-ATLAS. The S/UNI-ATLAS is configured and controlled through a generic 16-bit asynchronous microprocessor bus.

The S/UNI-ATLAS is implemented in low power 3.3 Volt CMOS technology. The microprocessor and JTAG interfaces are 5 Volt/ 3.3 Volt tolerant, while all other interfaces are 3.3 Volt only. The S/UNI-ATLAS is packaged in a 432-pin SBGA package.

**ISSUE 4**

DSLAM REFERENCE DESIGN: CORE CARD

For a more detailed description of the S/UNI-ATLAS, see the S/UNI-ATLAS Datasheet, PMC-971154 document [4].

#### 5.1.1. Ingress SRAM

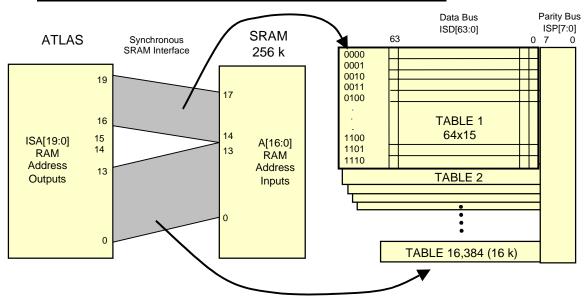

The Ingress VC Table is stored externally to the S/UNI-ATLAS in SRAM (Static RAM). The ingress SRAM data bus is 72 bits wide (8 bytes plus byte parity), with an address space of 20 bits (1 M). This creates enough context address space for 64 k VCs. The entire SRAM space does not have to be populatedr. If fewer than 64 k VCs are required or a subset of the S/UNI-ATLAS features are used, then the SRAM may be saved. The Ingress VC Table rows marked as 1011, 1100, 1101, and 1110 may be skipped. (In some isolated cases, mostly with older RAMs, glue logic may be required.)

Figure 8 shows an example of a connection of a Synchronous SRAM 20-bit wide address interface on the S/UNI-ATLAS into a 256 k 17-bit wide address SRAM. This configuration allows 16 k of VC Tables. The figure also shows addressing structure of a VC Table.

#### Figure 8. S/UNI-ATLAS SRAM VC Table Addressing

The four most significant bits in the ISA bus, ISA[16:19] *must always* be connected. Those bits point to a data row in the VC Table. The least significant portion of the address space can be used as required for each application. The above example uses 14 bits (ISA[13:0]) for the table address. The address space in the example allows addressing for  $2^{14}$  (16 k) VC Tables. Bits 14 and 15 are unconnected.

The total RAM space required for the above example is calculated as follows: (64 + 8) x 15 x 16384 = 17,694720 bits. Two 256 k 36-bit wide RAM devices allow storage of 262,144 x 36 x 2 = 18,874,368 bits. This is provided using one bank of two 256 k by 36 SSRAMs to make up the 72-bit wide data path. As there is only one bank of SSRAM, there is no address decode necessary.

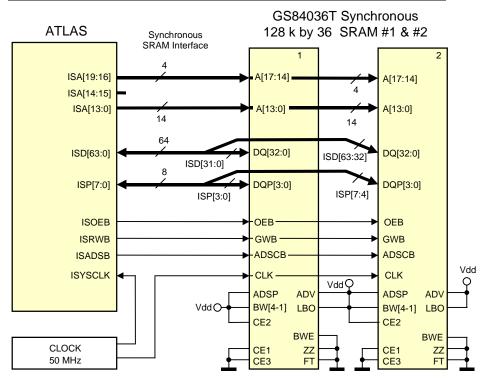

The Reference Design uses two GS88036T 256 k by 36 Synchronous SSRAMs manufactured by GSI Technology, Inc. A 100-pin TQFP package was chosen. Figure 9 shows the Ingress S/UNI-ATLAS to the SSRAM interface.

Figure 9. VC Ingress S/UNI-ATLAS-SSRAM Connection

For more information about how other configurations can be implemented, see the appendix in the S/UNI-ATLAS data sheet document, *Interfacing SSRAM to the S/UNI-ATLAS*. The appendix describes SSRAM configurations and several examples. The appendix also lists SSRAMs from various manufacturers that are compatible with the S/UNI-ATLAS and with this design in particular. For the S/UNI-ATLAS, synchronous flow-through (non-pipelined) SSRAMs must be used.

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

#### 5.1.2. Egress RAM

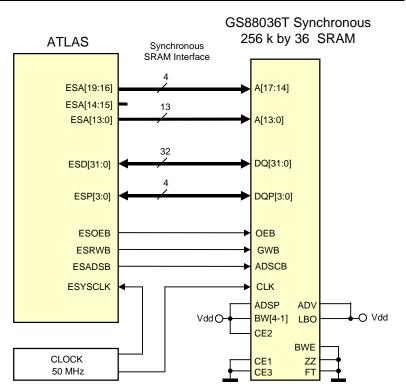

The Egress VC Table is stored external to the S/UNI-ATLAS in SSRAM. The addressing structure is similar to the ingress addressing shown in Figure 8. The egress SSRAM data bus is 36 bits wide (4 bytes plus byte parity), with an address space of 20 bits (1 M). This provides for 64 k connections, as with the Ingress VC Table. If fewer than 64 k connections are required or a subset of S/UNI-ATLAS features are used, then SRAM may be saved.

The Core Card Reference Design has enough SRAM to support 16 k connections at the egress port. This is provided using one 256 k by 36 SRAM (1 MB). As there is only a single SSRAM, no address decode is necessary. For the S/UNI-ATLAS, synchronous flow-through, non-pipelined SSRAMs must be used.

The Reference Design uses a GS88036B 256 k by 36 Synchronous SRAM manufactured by GSI Technology, Inc. (in a 100-pin TQFP package).

Figure 10 shows the egress S/UNI-ATLAS – SSRAM interface.

Figure 10. VC Egress S/UNI-ATLAS-SSRAM Connection

The four most significant bits in ESA bus, ESA[16:19] must always be connected.

RELEASED REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

DSLAM REFERENCE DESIGN: CORE CARD

For more bus termination and signal integrity examples, see section 11 in this document.

#### 5.2. S/UNI-APEX

#### 5.2.1. Functional Description

**ISSUE 4**

The PM7326 S/UNI APEX is a full duplex ATM traffic management device, that provides cell switching, per-VC queuing, traffic shaping, congestion management, and hierarchical scheduling for up to 2048 loop ports and up to four WAN ports.

The S/UNI APEX provides per-VC queuing for 64K VCs. A per-VC queue may be allocated to any Class of Service (COS), within any port, in either direction (ingress or egress path). Per-VC queuing enables PCR or SCR per-VC shaping on WAN ports and greater fairness of bandwidth allocation between VCs within a COS.

The S/UNI APEX provides three level hierarchical scheduling for port, COS, and VC level scheduling. There are two, three-level schedulers—one for the loop ports and one for the WAN ports. The three-level scheduler for the WAN ports provides:

- Weighted Interleaved Round Robin (WIRR) scheduling across the four WAN ports that enables bandwidth allocation selection between the ports.

- Priority Fair scheduling across the four COSs within each port. This class scheduler is a modified priority scheduler that allows minimum bandwidth allocations to lower priority classes within the port. Class scheduling within a port is independent of activity on all other ports.

- Three types of VC schedulers. VC scheduling within a class is independent of activity on all other classes

- Shaped fair queuing is available for four classes. If the COS is shaped, each VC within the class is scheduled for emission based on its VCs shaping rate. During class congestion, the VC scheduler may lower a VC rate in proportion to a normalization factor calculated as a function of the VC rate and the aggregate rate of all active VCs within the class.

- Weighted Interleaved Round Robin scheduling in which weights are used to provide fairness between the VCs within a class.

REFERENCE DESIGN PMC-1990815

**ISSUE 4**

**VORTEX CHIPSET**

DSLAM REFERENCE DESIGN: CORE CARD

- Frame continuous scheduling where an entire packet is accumulated before it is transferred to a class queue.

The three-level scheduler for the loop ports provides weighted Interleaved Round Robin (WIRR) scheduling. This scheduling, across the 2048 loop ports, enables bandwidth allocation selection between the ports and ensures that minimal PHY layer FIFOing is required to support a wide range of port bandwidths. Supported port bandwidths are from 32 kb/s to 52 Mb/s.

Priority scheduling across the four COSs within each port. Class scheduling within a port is independent of activity on all other ports.

VCs within a class are scheduled with a Round Robin scheduler or Frame Continuous scheduling. VC scheduling within a class is independent of activity on all other classes. Shaping is not supported on loop ports.

The S/UNI APEX forwards cells through tail of queue enqueuing and head of queue dequeuing (emission), where tail of queue enqueuing is controlled by the VC context record and subject to congestion control, and head of queue dequeuing is controlled by the three level hierarchical schedulers. The VC context record allows for enqueuing to any queue associated with any port and supports full switching from a port to port.

The S/UNI APEX supports up to 256 k cells of shared buffering in a 32-bit wide SDRAM. Memory protection is provided through an inband CRC on a cell by cell basis. Buffering is shared across direction, port, class, and VC levels. The congestion control mechanism provides guaranteed resources to all active VCs, allows sharing of available resources to VCs with excess bandwidth, and restricts buffer allocation on a per-VC, per-class, per-port, and per-direction basis. The congestion control mechanism supports PPD and EPD on a CLP0 and CLP1 basis across per-VC, per-class, per-port, and per-direction structures. EFCI marking is supported on a per-VC basis. Congestion thresholds and packet awareness is selectable for each connection.

The S/UNI APEX provides flexible capabilities for signaling, management, and control traffic. Four independent uP receive queues exist where both cell and AAL5 frame traffic may be enqueued for termination by the uP. A staging buffer is also provided enabling the uP to enqueue both the cell and AAL5 frame traffic to any outgoing queue. AAL5 SAR assistance is provided for AAL5 frame traffic to and from the uP. AAL5 SAR assistance includes the generation and checking of the 32-bit CRC field and the ability to reassemble all the cells from a frame in the VC queue before placement on the uP queues. Any or all of the 64 k VCs may be configured to be routed to/from the uP port. Any or all of the VCs configured to be routed to/from the uP port may also be configured for AAL5 SAR assistance

**VORTEX CHIPSET**

ISSUE 4

simultaneously. OAM cells may be routed optionally (per-VC selectable) to a uP receive queue or switched with the user traffic. CRC10 generation and checking is optionally provided on OAM cells to and from the uP.

The S/UNI APEX maintains cell counts of CLP0 and CLP1 cell transmits on a per-VC basis. Global CLP0 and CLP1 congestion discards are also maintained. Various error monitoring conditions and statistics are accumulated or flagged.

The uP has access to both the internal S/UNI APEX registers and the context memory, as well as diagnostic access to the cell buffer memory.

The S/UNI APEX provides a 16-bit wide Any-PHY compliant loop side master/slave interface that supports up to 2048 ports. Egress cell transfers across the interface are identified through an inband port identifier prepended to the cell. To accept the cell, the slave devices must match the inband port identifier with their own port ID or port ID range. Per port egress flow control is executed through a 12-bit address polling bus to which the appropriate slave devices respond with out-of-band per port flow control status. Ingress cell transfers across the interface is executed through a combination of UTOPIA L2 flow control polling and device selection for up to 32 slave devices. The Any-PHY loop side interface may be reconfigured as a standard single port 16-bit wide Any-PHY or UTOPIA L2 compliant slave interface. The 16-bit prepends are supported optionally on both ingress and egress for cell flow identification, enabling use with external address resolution devices, switch fabric interfaces, or other layer devices.

The S/UNI APEX provides an 8- or 16-bit Any-PHY or UTOPIA L2 compliant WAN side master interface that supports up to four ports. The 16-bit prepends are supported optionally on both ingress and egress for cell flow identification, enabling use with external address resolution devices, switch fabric interfaces, or other layer devices.

The S/UNI APEX provides a 32-bit microprocessor bus interface for signaling, control, cell, and frame message extraction and insertion, VC Class and port context access, control and status monitoring, and configuration of the IC. Microprocessor burst access is supported for registers, cell and frame traffic...

The S/UNI APEX provides a 36-bit SSRAM interface for context storage that supports up to 4 MB of context for up to 64 k VCs and up to 256 k cell buffer pointer storage. Context Memory protection is provided with 2 bits of parity over each 34-bit word.

The total number of cells, the total number of VCs, support for address mapping, and shaped fair queuing is limited to the amount of context and cell buffer

REFERENCE DESIGN PMC-1990815

DSLAM REFERENCE DESIGN: CORE CARD

memory available. Table 1 shows the most common combinations of memory and features.

| Context Memory<br>Size<br>ZBT SSRAM | Cell Buffer<br>Memory Size<br>SDRAM | # VC | # Cell<br>Buffers | Address<br>Mapping<br>Support | Shaping<br>Support |

|-------------------------------------|-------------------------------------|------|-------------------|-------------------------------|--------------------|

| 1 MB                                | 4 MB                                | 16 k | 64 k              | Yes                           | No                 |

| 2 MB                                | 4 MB                                | 16 k | 64 k              | Yes                           | Yes                |

| 2 MB                                | 4 MB                                | 64 k | 64 k              | No                            | No                 |

| 4 MB                                | 16 MB                               | 64 k | 256 k             | Yes                           | Yes                |

**TABLE 1.** Feature Set as a Function of Memory Capacity

**ISSUE 4**

NOTE: The table may not correspond to the final settings on the Core Card due to RAM availability and other reasons. Designers should follow the RAM size recommendations outlined in the above table and in the calculations presented in document [12].

The Reference Design Core Card supports the layout for 4 MB of Context Memory SSRAM and 16 MB of Cell Buffer SDRAM, thus allowing 64 k of VCs and 256 k of buffered cells. The maximum RAM size was chosen for evaluation purposes and interface verification. However, due to RAM availability, the Core Card may be populated with smaller size NBT RAM. Board inspection is required to determine actual RAM size. The RAM interfaces are described in following sections.

The S/UNI-APEX provides facilities to enable sparing capability with another S/UNI-APEX device. The facilities enable a *warm standby* capability, in which connection setup between the two devices can be maintained identically but some cell loss occurs at the point of device swapping. The facilities do not include a cell-by-cell lock step between the two S/UNI-APEX devices. To avoid any cell replication, queues in the *spare* S/UNI-APEX are kept empty, causing all queued traffic in the *active* S/UNI-APEX to be lost at the point of switch over. Since connection setup is maintained identically between the two S/UNI-APEX devices, switch over can happen instantaneously allowing you to avoid connection timeout or teardown issues.

The S/UNI-APEX facilities provided are the disable and filter control bits in the Receive and Transmit Control register. These control bits are asserted in the spare S/UNI-APEX to ensure the queues remain empty until swapping is initiated. Alternatively, asserting only the Filter enable bits allow signaling and control traffic continuity to be maintained to the spare S/UNI-APEX. This enables

DSLAM REFERENCE DESIGN: CORE CARD

datapath integrity testing on the spare plane and ensures control communications paths to the spare plane are usable.

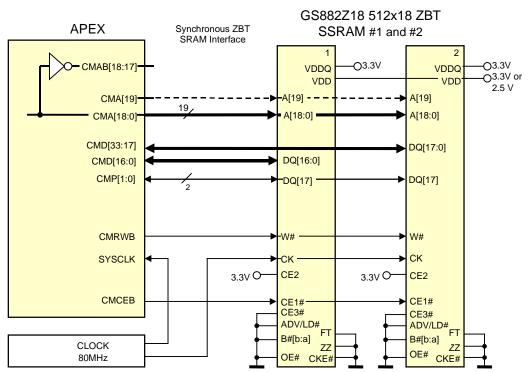

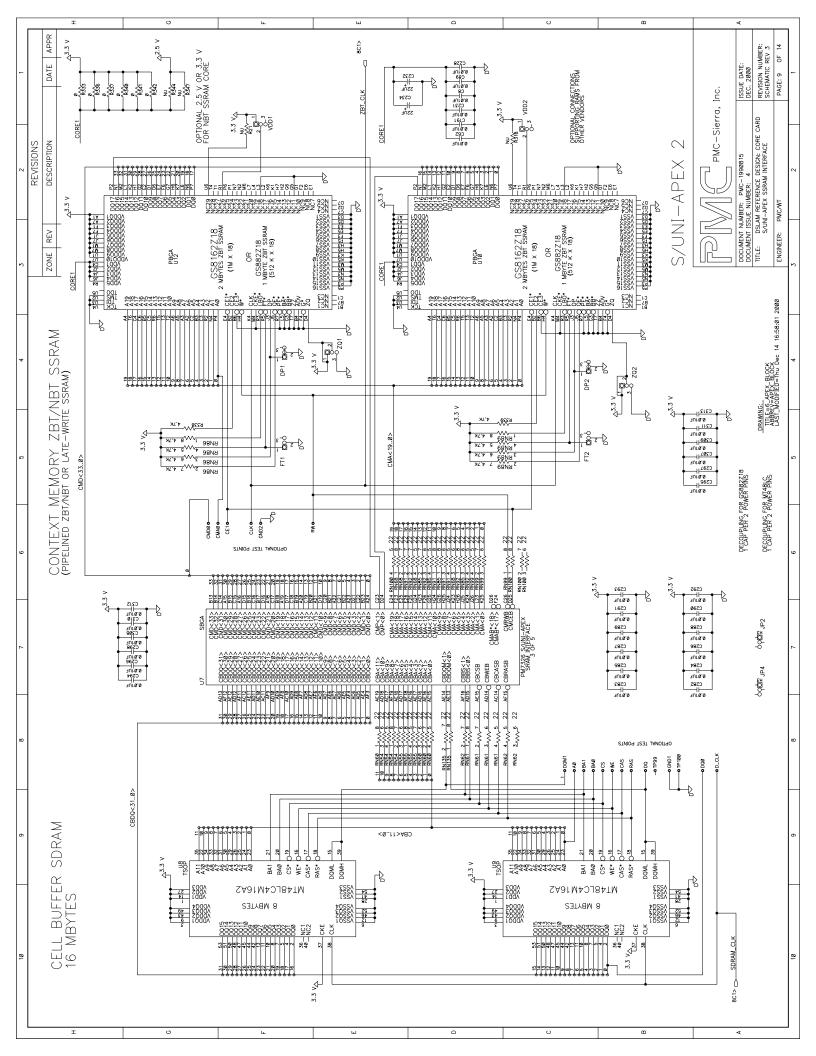

#### 5.2.2. Context Memory SSRAM Interface

The S/UNI-APEX context memory SSRAM interface can be configured for two types of synchronous RAMs: *Late Write* or *Zero Bus Turnaround*<sup>™</sup> (also known as NBT). The Core Card is assembled with a pipelined ZBT/NBT SSRAM. Schematic and board layout support optional placement of a RAM, up to 2 Mbytes each with address lines CMA<19..0> connected. Also, the layout supports the RAM core supply at 2.5 V for GS8162Z18 (the pinout is preliminary at the time this document is created, and pinout verification is advised). The GS162Z18 option requires zero-ohm resistor that strap 2.5 V to the CORE1 rail. Other RAMs from Samsung and possibly from IDT and Cypress may be placed with minimum rework on the board. Schematic and layout, of the Core Card Reference Design Issue. 3, supports only GSI GS882Z18 NBT RAM without any strapping. RAMs are set in a single bank that consist of two 512 M x 18 ZBT SRAMs (1 MByte each) and provide 2 MB of SSRAM memory.

The SSRAM bus is clocked at 80 MHz. Signal integrity simulation and timing simulation was done to derive design guidelines. Serial termination resistors are inserted in data path to attenuate backreflections and improve signal integrity. For more examples on bus termination and signal integrity, see Section 11, *Bus Termination Examples*, in this document.

The S/UNI-APEX SSRAM address bus CMA[19:0] is connected with all lines that allow an address up to 1,048,576 (1 M). CMCEB is used to control chip selection on RAMs.

The data bus CMD[33:0] is split into lower and upper chunks and connected to respective SSRAM devices. Each 17-bit wide segment is associated with a parity bit CMP[0] or CMP[1], which are connected to the corresponding DQ[17:0] 18-bit wide ports on the SSRAM devices. The S/UNI-APEX generates the parity bit , which is stored into RAM.

The OE# inputs on the SSRAM is tied to ground. The read/write line CMRWB determines if the data bus is in a read or write cycle. For more information about bus timing, see Section 11, *Bus Termination Examples*, in this document.

If the S/UNI-APEX detects a parity error, the two parity bits protecting the 34-bit data bus can trigger an interrupt at the S/UNI-APEX. Parity check generation can be used to detect data corruption in highly reliable data transfer protocols or networks.

DSLAM REFERENCE DESIGN: CORE CARD

Figure 11 shows the S/UNI-APEX to the SSRAM interface.

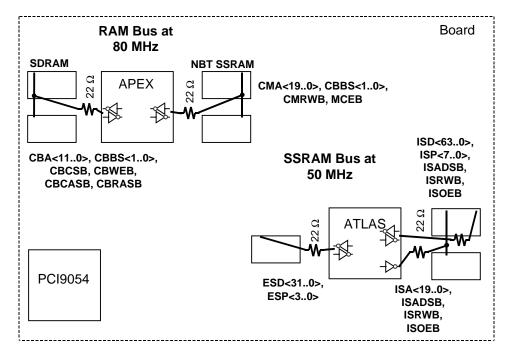

### Figure 11. Dual Bank Configuration for ZBT SSRAM

For examples of a generic interface to SSRAM, see the S/UNI-APEX data sheet.

The Core Card schematic Issue 3 on page 9 shows an optional core supply with 2.5 V for larger NBT SSRAMs. The board is laid out with a copper cutout underneath the RAMs, allowing a 3.3 V or 2.5 V supply with different resistors placement on assembly line. The Core Card printed circuit board Rev. 3 is assembled with a 3.3 V version of NBT SSRAM. The designer should evaluate the availability of RAMs, and possibly choose to eliminate the 2.5 V supply by shorting the copper cutout to 3.3 V.

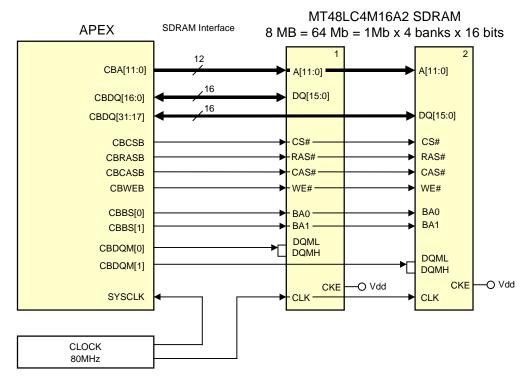

#### 5.2.3. Cell Buffer SDRAM Interface

The Reference Design shows the S/UNI-APEX with 16 MB of SDRAM for queued cell buffering. The SDRAM buffer consists of a single bank with two RAMs for a 32-bit wide data path that provides room for up to 64 k cells. The SDRAMs are Micron's MT48LC4M16A2TG 8 MB (size derived from 1 Mb x 16 x 4 banks = 64 kb = 8 MB). PMC-1990815

**VORTEX CHIPSET**

DSLAM REFERENCE DESIGN: CORE CARD

The S/UNI-APEX allows CRC-16 check on the first 60 bytes in per-cell basis of the data from the SDRAM. If an error occurs, an interrupt is sent to the microprocessor.

Figure 12 shows an example of a 16 MB SDRAM.

#### Figure 12. Single Bank SDRAM 4 MB for 64 k Cells

The data mask signals CBDQM[1:0] at the S/UNI-APEX control the read/write cycle on the CBDQ[31:0] bus.

The S/UNI-APEX and SDRAMs run at 80 MHz for the Core Card. Bus termination and signal integrity examples are shown in this document in Section 11, *Bus Termination Examples*,

#### 5.3. S/UNI-VORTEX

The PM7351 S/UNI-VORTEX is a monolithic integrated circuit typically used with its sister device, the S/UNI-DUPLEX, to implement a point-to-point serial backplane interconnect architecture.

Multiple S/UNI-VORTEX devices can reside on a common cell processing card beside a traffic management device. The traffic management device exchanges

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

cells with the S/UNI-VORTEX through a 16-bit wide SCI-PHY or Any-PHY interfaces (bus). The flow control is affected across this interface through cell available signals that the S/UNI-VORTEX generates. In the downstream direction, the traffic management device can poll for the availability of a buffer for each logical channel. In the upstream direction, an indication is provided whether one or more cells are queued in the S/UNI-VORTEX for transfer.

Each S/UNI-VORTEX can be connected to eight Line Cards through high-speed 100 to 200 Mb/s serial links. Each upstream link has its own queue. If a queue becomes nearly full, a flow control indication is sent downstream. In the downstream direction, each logical channel has a dedicated cell buffer to avoid head of line blocking. The serialization of cells from the cell buffers is throttled by flow control information sent from the line card through the upstream high-speed link.

A microprocessor port provides access to internal configuration and monitoring registers. That port can also be used to insert and extract cells in support of a control channel.

#### LVDS INTERFACES, BOTH DIRECTIONS:

- Eight independent four-wire LVDS serial transceivers, each operating at up to 200 Mbps across PCB or backplane traces or across up to 10 meters of four-wire twisted pair cabling for inter-shelf communications.

- Usable bandwidth (excludes system overhead) of 186 Mbps, for each direction of each LVDS link.

- Fully integrated LVDS clock synthesis and recovery. No external analog components are required.

#### RECEIVE DIRECTION:

- Weighted round-robin multiplex of cell streams from the eight LVDS links into a single cell stream that is transferred to the parallel bus under control of the bus master.

- LVDS link and S/UNI-VORTEX identifiers that are added to each cell (along with the PHY identifier already added by S/UNI-DUPLEX) for use by the ATM layer to identify the cell source.

- Back-pressure that is sent to the far end to prevent an overflow of the receiver FIFO.

#### TRANSMIT DIRECTION

Per-PHY and microprocessor port back-pressure that are used on each of the eight links to prevent the overflow of downstream buffers. RELEASED REFERENCE DESIGN

PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

- Device polling that provides Utopia-like TCA status for 264 PHYs (includes 8 control channels), based on back-pressure from the LVDS links.

- Cell transfer, where the bus master adds a PHY address to each cell through a 12-bit identifier. The S/UNI-VORTEX decodes and accepts the cells for its links, based on software-configured base addresses.

# PARALLEL BUS INTERFACE:

- Both directions: 16-bit wide, 50 MHz maximum clock rate, bus slave.

- Cells transferred to the bus Utopia L2 compatible with optional expanded length cells. The cell appears as from a single PHY, with a cell prepend that identifies the source PHY ID of each cell. Alternatively, Utopia L2 compliance is supported by placing the PHY ID inside the UDF/HEC fields of a standard ATM cell.

- Cells received from the bus. The Any-PHY bus is similar to Utopia L2, however with optional expanded length cells and expanded addressing capabilities. The S/UNI-VORTEX appears to the bus master as a 264port, multi-PHY device (eight links, each with 32 PHYs & a communication channel). The PHY address is added as the cell prepend or optionally in the HEC/UDF field when standard length cells are desired.

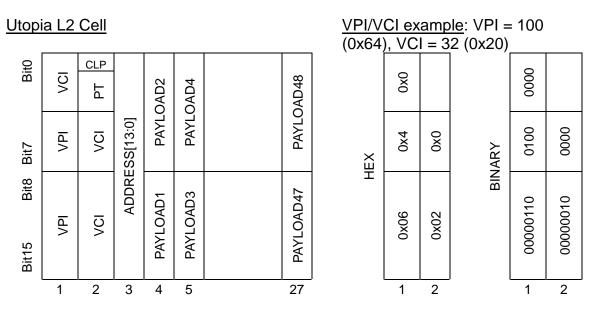

Example of a 16-bit wide UTOPIA L2 cell is shown below.

Core Card software driver applications sets UL2 bus to have word 3 overwritten with logical channel ID from S/UNI-VORTEX and phy ID from S/UNI-DUPLEX.

DSLAM REFERENCE DESIGN: CORE CARD

#### MICROPROCESSOR INTERFACE

• 8-bit data bus, 8-bit address bus.

**ISSUE 4**

- Provides read/write access to all configuration and status registers.

- Provides CRC32 calculation and cell transfer registers to support an embedded microprocessor-to-microprocessor communication channel over the LVDS link.

# 5.4. S/UNI-DUPLEX

The PM7350 S/UNI-DUPLEX is a monolithic integrated circuit typically used for traffic concentration within a DSLAM. The device is ATM specific. It exchanges contiguous 53 byte cells with PHY devices. The PHY interface can be either clocked serial data or SCI-PHY/Any-PHY.

A clocked serial data configuration of up to sixteen channels is supported. Cell alignment is established through HCS (Header Check Sequence) delineation. The cell payload is scrambled and descrambled with a  $x^{43}$  + 1 polynomial. Rate adaptation is performed through idle cell insertion and extraction. Each PHY interface has a dedicated four-cell FIFO in both upstream and downstream directions.

All cell streams are multiplexed into a high-speed serial stream. Each S/UNI-DUPLEX can connect to two 100 to 200 Mb/s Low Voltage Differential Signal (LVDS) serial links. The internal transmit clock is synthesized from a lower frequency reference run at 1/8 of the line rate. An extended cell format provides four extra bytes for the encoding of flow control, timing reference, PHY identification, and link maintenance information. A redundant link is provided to allow connection to two cell processing cards.

A microprocessor port provides access to internal configuration and monitoring registers. The port may also be used to insert and extract cells in support of a control channel.

The S/UNI-DUPLEX is typically used with its sister device, the S/UNI-VORTEX, to implement a point-to-point serial backplane interconnect architecture.

For more information about S/UNI-DUPLEX, see the S/UNI-DUPLEX Datasheet.

REFERENCE DESIGN PMC-1990815

ISSUE 4

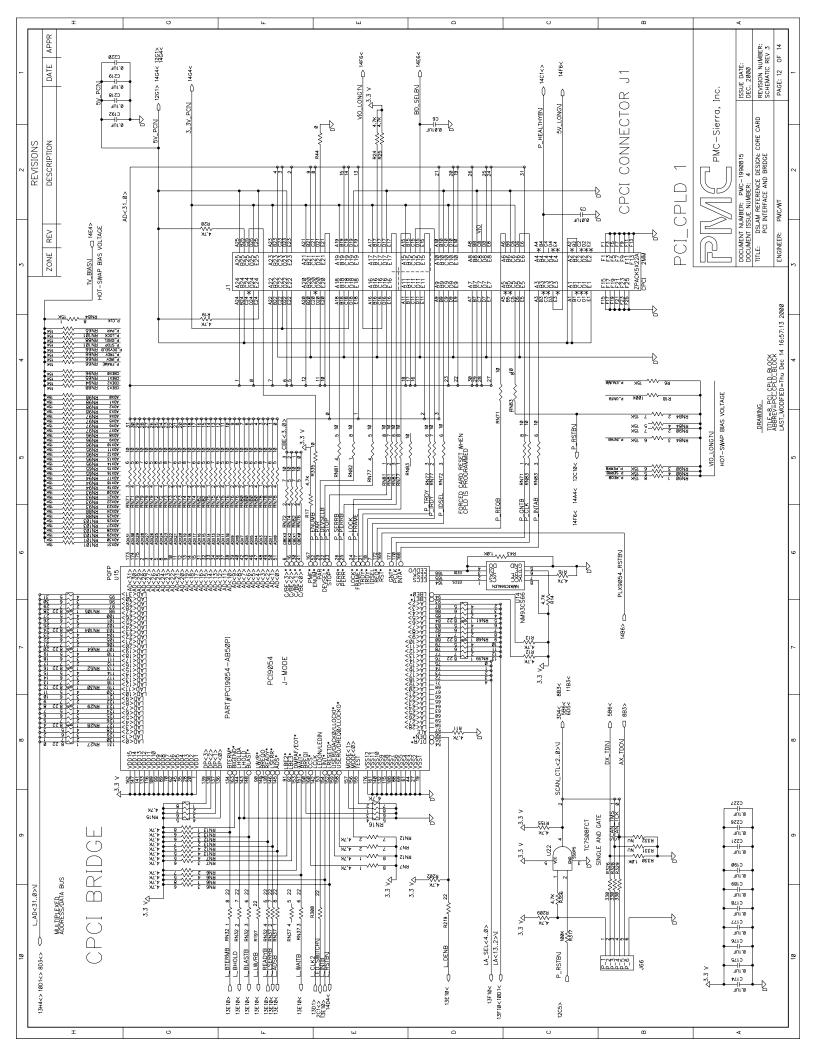

# 5.5. CPCI Bridge

This section briefly introduces the cPCI bridge functionality.

# 5.5.1. PCI9054 PCI Bridge

To interface the VORTEX chipset residing in the Core Card to the host CPU residing in slot 1 of the cPCI shelf, a PCI-to-Local-bus bridging device is required. The device chosen for this Reference Design is the PLX PCI9054 PCI Bus Master I/O Accelerator Chip. Some features that were deciding factors in becoming the bridge of choice for this Reference Design are:

- PCI v2.2 compliant 32-bit 33 MHz Bus Master Interface Controller that enables PCI Burst Transfers up to 132 Mbytes/second

- General Purpose Bus Master Interface featuring an advanced Data Pipe Architecture<sup>™</sup> which includes two DMA engines, programmable Target and Initiator data transfer modes and PCI messaging functions

- PCI v2.2 Power Management Spec compatible

- Flexible +3.3 V, +5 V Tolerant Local Bus operation up to 50 MHz

- 32-bit multiplexed, or non-multiplexed local bus supporting 8-, 16-, and 32-bit peripheral and memory devices

- CompactPCI hot-swap capability

Since the S/UNI-APEX requires a multiplexed bus, for this Reference Design, the PCI 9054 bridge is programmed to perform in a 32-bit multiplexed mode (J mode). The fact that the S/UNI-APEX is a 32-bit device, the S/UNI-ATLAS is a 16-bit device, and the S/UNI-VORTEX and S/UNI-DUPLEX are both 8-bit devices adds complexity to the local bus, on which they all reside. While the local bus can support 8-, 16-, and 32-bit devices, for this Reference Design, the PCI 9054 operates solely in 32-bit mode. (For more information, see section 8.4.)

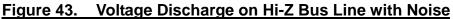

# 5.5.2. SEEP Basics

The PCI 9054 provides a serial EEPROM (SEEP) port for loading configuration information on power-up and reset. The SEEP is programmed with address space boundaries for the VORTEX chipset and the Core Card IDs. The CPLD is used with the PCI9054 to provide address decoding and microprocessor port control for the DSLAM chips being accessed from the PCI bus. For more information about SEEP, see sections 8.6 and 8.7.

Examples of data reading on reset are shown in section 16 APPENDIX C: EXAMPLE OF SEEP READING ON RESET in this document.

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

# 6. SIGNAL FLOW ON THE CORE CARD IN BRIEF

#### 6.1. Upstream Direction

The following process refers to the VORTEX Chipset Driver defaults or test routines, for example, the cells on Utopia L2 into the S/UNI-ATLAS Ingress are 27 words with the ID written into the HEC/UDF word.

Cells that originate from a Comet or PHY device on the Line Cards and are destined for the WAN Card are manipulated in the following manner:

- Upstream cells are received by the PHY and buffered until the S/UNI-DUPLEX reads them. As a cell is read from the PHY, the S/UNI-DUPLEX writes the originator PHYID[4:0]—or microprocessor ID, in the case of the embedded Inband Communication Channel (ICC)—into the LVDS data structure and sends the cell through the LVDS serial link to its corresponding S/UNI-VORTEX on both the active and stand-by Core Cards.

- The S/UNI-VORTEX receives cells by servicing its eight links in a simple weighted round-robin fashion. As the S/UNI-VORTEX reads cells from the high-speed serial link, it inserts into the HEC/UDF field the ADDR[13:0], which contains its own hardwired S/UNI-VORTEX ID VADR[4:0] (ADDR[13:9]), the high speed LINKID[2:0] (ADDR[8:6]), and the logical channel ADDR[5:0]. At this point, cells are available to the Scy-PHY/UL2 bus that connects the S/UNI-VORTEX to the S/UNI-ATLAS. (software test routines generate cells which are Utopia L2 compatible.)

- After an upstream cell is read in by the S/UNI-ATLAS, it will use the PHYID, LINKID, and VORTEX IDs to perform a lookup function that results in a short connection (or switch) tag being inserted into the HEC/UDF before passing it to the S/UNI-APEX. The S/UNI-APEX uses the tag to directly address the context and control information pertaining to the cell. The present test routines (supplementing VORTEX Chipset Driver) translate the header in the S/UNI-ATLAS.

- The S/UNI-APEX provides per-VC congestion control, buffering, and queuing, and provides switching and traffic shaping into four high-speed WAN up-link ports. Upstream traffic is passed from the S/UNI-APEX back through the S/UNI-ATLAS Egress. The S/UNI-ATLAS first provides counting and OAM functionality. Then the S/UNI-ATLAS transfers the data onto the Core Card's S/UNI DUPLEX to transmit over the LVDS serial link onto the WAN Card.

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

The S/UNI-DUPLEX on the Core Card first writes the destination PHY ID (3:0) (or EIC) into all cells. Then the S/UNI-DUPLEX transmits them to the S/UNI DUPLEX that resides on the WAN Card. The upstream traffic received by the WAN Card's S/UNI-DUPLEX is passed onto the card's S/UNI-QJET, which frames the data into DS3 format and sends it out over the appropriate (one of four) DS3 link.

# 6.2. Downstream Direction

The following process refers to the software driver defaults or test routines, for example, the cells on Utopia L2 into S/UNI-ATLAS Ingress are 27 words with the ID written into the HEC/UDF word.

Cells that originate from the WAN and are destined for a Line Card or PHY device are manipulated in the following manner:

- Data received by the WAN Card's four DS3 links is passed to the S/UNI-QJET which multiplexes the data, and sends it to the WAN Card's S/UNI-DUPLEX for transmission to the Core Card over the high-speed serial link. The WAN Card's S/UNI-DUPLEX writes the originator PHY ID (3:0) into the LVDS data structure before transmitting data to the CORE card.

- Downstream data received by the Core Card's S/UNI-DUPLEX is passed to the S/UNI-ATLAS. The cells proceed through the S/UNI-ATLAS and onto the S/UNI-APEX, where all ATM layer functions are performed on the cells. The S/UNI-APEX appends to all PHY-destined cells a unique 12-bit address that identifies the destination S/UNI-VORTEX, LINK, and PHY IDs (or S/UNI-VORTEX, LINK, and the EIC). The data is then placed on the ANY-PHY bus that connects the S/UNI-VORTEX devices to the ATM layer of the DSLAM shelf. The present test routines (supplementing Chipset Driver) translate header in the S/UNI-ATLAS.

- The 12-bit address is used by the S/UNI-VORTEX devices that are connected to the ANY-PHY bus to determine whether or not a cell placed on the bus is destined for them; if they are, then the cell should be read.

- Downstream cells received by the S/UNI-VORTEXes are stripped of the prepended address segment. The S/UNI-VORTEX writes the destination PHY ID into the LVDS data structure and sends cells across the appropriate LVDS serial link (7:0) to the corresponding S/UNI-DUPLEX device that resides on the Line Card.

- The Line Card's S/UNI-DUPLEX device, after receiving cells from the high-speed serial interface, strips the prepended bytes from the cells and sends the data to the appropriate PHY (or to the microprocessor in the case of the ICC).

REFERENCE DESIGN PMC-1990815 PMC-Sierra, Inc.

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

## 7. HOT SWAP

The Core Card has been designed to be hot-swap compatible. The Hot Swap Specification [19] states: "The basic purpose of the Hot Swap addition to CompactPCI is to allow the orderly insertion and extraction of boards without adversely affecting system operation."

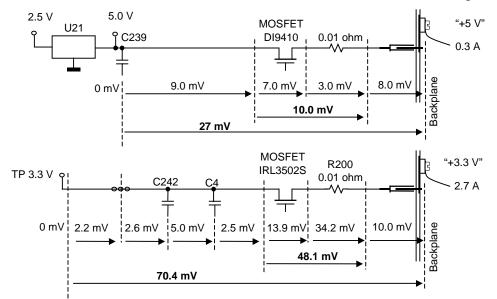

# 7.1. cPCI and Power Rail Hot Swap

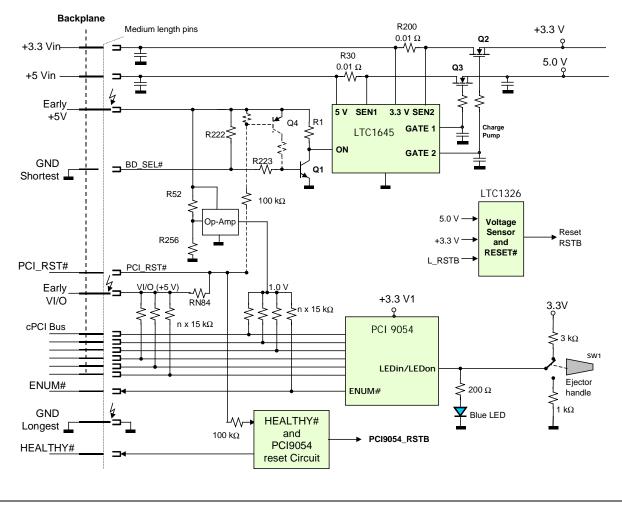

The Core Card uses a hot-swap compatible cPCI bridge, PLX PCI9054, and a hot-swap controller, the Linear Technology LTC1654. The cPCI connector is assembled with three different length pins, as required by the Hot Swap Specification [19]. The supporting circuitry is also carefully designed to not impair the hot-swap ability. Figure 13 shows an example of the hot-swap circuit.

Figure 13. Example of a Hot-Swap Circuit

REFERENCE DESIGN PMC-1990815

**VORTEX CHIPSET**

ISSUE 4

DSLAM REFERENCE DESIGN: CORE CARD

The above figure shows that the card is about to be placed into the shelf. The first three mating pins are: the longest GND (ground), the longest +5V (if cPCI is +5 V environment), and long VI/O. The longest +5V pin is also called *early 5 V*. In a 3.3 V environment, it is referred to as *early 3.3 V*. The early VI/O polarizes some of the cPCI bus pins with +5V through 15 kohm resistors. The early +5V flows into a network of resistors and transistors. The current is limited to few mA. The